## Teledyne

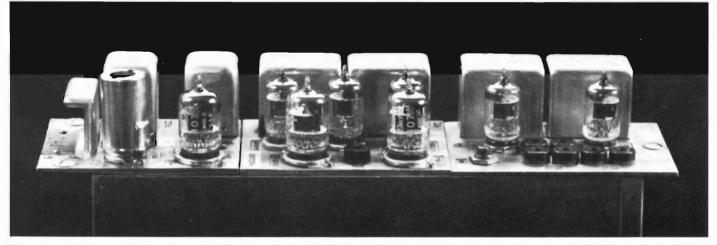

# Junction FETs Theory and Applications

#### INTRODUCTION TO APPLICATION NOTES

The applications material presented on the following pages is intended for the use of the serious engineer with a basic circuit design task. It is not meant as a "hookup guide" for the casual hobbyist wishing to wire up a preamp.

Terminology used throughout these pages is consistent with that presented in the tabular data listings for various devices. Where the reader encounters a new term, he will find an explanation in the glossary elsewhere in this book.

Most of the information presented here has been developed in the application laboratories of Teledyne Semiconductor. A few sections had been published previously in technical magazines and edited or revised for this publication. Where material has been "borrowed" from outside sources, appropriate credit is appended as a note at the proper place.

Some of the most complicated design problems have the most simple solutions: if you think you know how the circuit should look, but aren't positive, you may find it expedient to obtain a sample device from a Teledyne Semiconductor sales office or representative and prepare a breadboard circuit. Strip away the symbology and you'll discover that JFETs are easy to use.

## **Junction FETs Theory and Applications**

#### INTRODUCTION

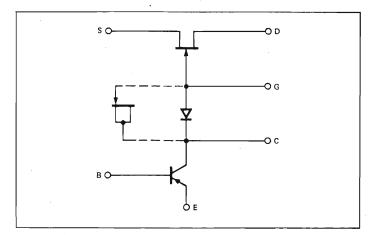

The field effect transistor (FET), is a device whose operation differs radically from the NPN or PNP injection type transistor although both are called transistors. The FET is a majority carrier device while the injection type is a minority carrier device. The former is based on the properties of reverse biased pn junctions while the latter depends on a combination of reverse biased and forward biased pn junctions. Both are three terminal elements although some FET's can be made as four terminal devices without affecting the basic operation of the device.

The properties of field effect and injection transistors differs as follows:

#### A. Input Impedance:

- The FET is a high input impedance device, since the input terminal is essentially looking into a reverse biased junction.

- The injection type transistor is a low input impedance device because the input is basically a forward biased diode.

#### B. Mode of Operation:

- 1) The FET is a voltage controlled device just as is a vacuum tube pentode.

- The injection transistor is a current controlled device.

#### C Output Impedance:

- The FET is a high output impedance device, or current source, although different means of manufacturing may result in relatively low output impedance.

- 2) The injection type transistor is also a high output impedance device, though not as "stiff" as the field effect because of the Early Effect which results in both a decreasing output impedance and a variation in gain with collector voltage.

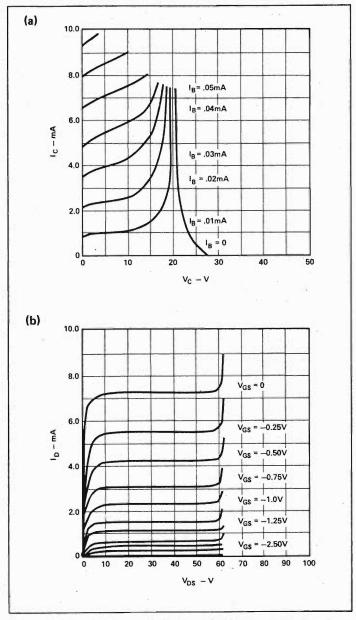

These characteristics can be summarized in Fig. 1 which gives a comparison between typical transistors and FET's.

#### MODE OF OPERATION

The three terminals of the FET are referred to as the "source," the "gate" and the "drain," corresponding to the emitter, base and collector of the transistor, respectively, or in vacuum tube terminology, to the cathode, grid and anode, respectively.

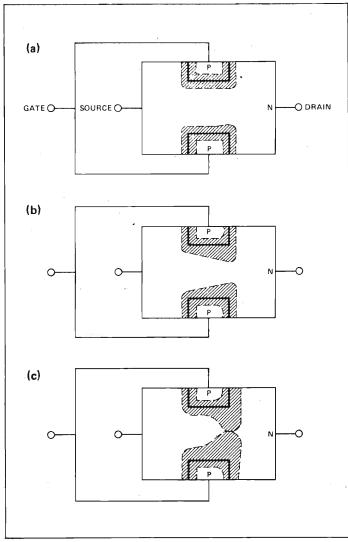

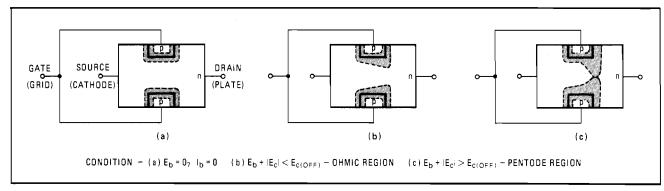

Fig. 2 shows schematically the cross section of an Nchannel FET. The operation of the FET depends on the modulation of the resistance of the current path (or channel) through N type material between the source and drain contacts. This modulation is achieved by means of two P type regions (usually tied together) - the gate. When the PN junctions limiting the channel are biased in the reverse direction, the cross section of the channel is modulated by the penetration of the depletion layers of the junctions (shown by cross hatched areas in Fig. 2). Essentially no current is allowed to flow through these depletion layers except for the very small amount that constitutes the leakage of the reverse biased diodes. If the junctions are of the exponentially graded type, the penetration of the depletion layers into the channel follows a square law characteristic. When the reverse bias is so large as to cause the two depletion layers to join, the channel is said to be "pinched off," and the conductivity between source and drain drops to essentially zero.

Fig. 1. Electrical Characteristics for (a) Injection NPN Transistor, (b) Field Effect N-Channel Transistor

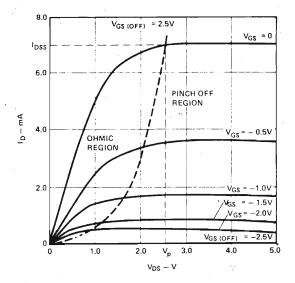

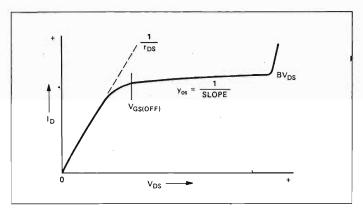

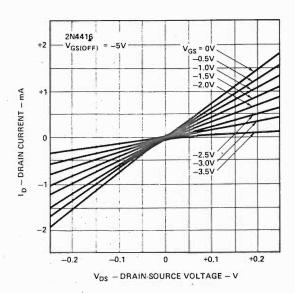

In the normal mode of operation of the device, the source is grounded, and voltages  $V_{DS}(>0)$  and  $V_{GS}(<0)$  are applied to the drain and the gate, respectively. For a given combination of these voltages, the depletion layers of the PN junctions exhibit a varying width along the channel (Fig. 2b), since the back biasing voltage is essentially  $\ensuremath{V_{\text{GS}}}$  at the left hand end of the channel, and  $V_{\text{DS}} + V_{\text{GS}}$  at its right hand end (neglecting voltage drops in the bulk of the source and drain regions). At sufficiently high voltages, the sum  $V_{DS}$  +  $V_{\text{GS}}$  at the right hand end of the channel equals the pinch off voltage, V<sub>P</sub> at which the channel becomes pinched off (Fig. 2c). Fig. 3 shows the drain characteristics of a typical unit, plotted for various gate voltages. The plot consists basically of two regions, the ohmic region and the pentode region. The boundary between the two regions (shown by the dotted curve) is the locus of points for which  $V_{DS}$  +  $V_{\text{GS}} = V_{\text{GS[OFF]}}$ . At low values of drain voltage the characteristics in the ohmic region are linear and describe the modulation of the channel conductance from its maximum

Fig. 2. Schematic Cross of Field Effect Transistor Showing Depletion Layers for

(a)  $V_{DS}=0$ ,  $I_{D}=0$ ; (b)  $V_{DS}+|V_{GS}| < V_{P}$  (Ohmic Region); (c)  $V_{DS}+|V_{GS}| > V_{P}$  (Pinch Off Region)

value 1/ro (ro being the channel resistance) to essentially zero when the gate voltage reaches the pinch off value,  $V_{\text{GS(OFF)}}$ . In the pinch off region, the channel is pinched off since  $V_{\text{DS}} + V_{\text{GS}}$  exceeds  $V_{\text{GS}(\text{OFF})}$  so that further increase of current is prevented when additional drain voltage is applied. In that region, the FET can best be described as a current limiter, the amount of current being again controlled by the gate voltage.

The pinch off voltage  $V_{\text{GS(off)}}$  can be deduced in two ways from the drain characteristics shown in Fig. 3, either as the voltage at which the  $V_{GS} = 0$  curve saturates to a constant pinch off current  $I_{DSS}$ , or as the smallest  $V_{GS}$  value for which drain current is shut off.

The drain current at any  $V_{\text{GS}}$  can be written as:

$$I_{\text{S}} = I_{\text{DSS}} \left( 1 - \frac{V_{\text{GS}}}{V_{\text{GS(OFF)}}} \right)^2$$

Another important parameter — in addition to V<sub>GS(OFF)</sub> and  $I_{\text{DSS}}$  — is the transadmittance  $Y_{\epsilon_0}$ . It is defined in the same way as for a vacuum tube as the change of drain (plate) current with gate (grid) voltage at constant drain (plate) voltage:

$$Y_{fs} = \frac{\partial I_D}{\partial V_{GS}} \Big|_{V_{DS}} = constant$$

Fig. 3. Drain Characteristics of Teledyne 2N3436 Field Effect Transistor in the Low Voltage Region.

The variation of transadmittance with gate voltage is inherent to the FET and, again in the case of exponentially graded junctions, varies as

$$\begin{split} Y_{fs} &= Y_{fso} \left( 1 - \frac{V_{GS}}{V_{GS\{OFF\}}} \right) \\ \text{where} \quad Y_{fso} &= - \frac{2 \, I_{DSS}}{V_{GS\{OFF\}}} \end{split}$$

$Y_{fso}$ , the transadmittance at  $V_{GS}=0$ , is the value usually included in the specifications of the device. The approximate relation between  $Y_{fso}$  and  $r_{ds}$  is

$$Y_{fso} = 1/r_{ds}$$

The output impedance  $r_{ds}$  (similar to the plate resistance of vacuum tubes) is:

$$r_{ds} = \frac{\partial V_{DS}}{\partial I_D} \left| V_{GS} = constant = \frac{1}{g_{os}} \right|$$

Since the FET acts as current limiter in the pinch off region,  $r_{ds}$  is very high ( $g_{os}$  very low).

As is the case for transistors, the maximum reverse bias between the gate and either the source or the drain is limited by the junction breakdown voltage V<sub>B</sub>. Breakdown characteristics have been included in the FET characteristics shown in Fig. 1, although such a range is beyond the maximum permissible voltage quoted by the manufacturer for normal operation.

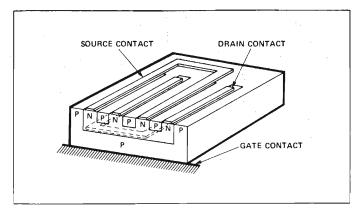

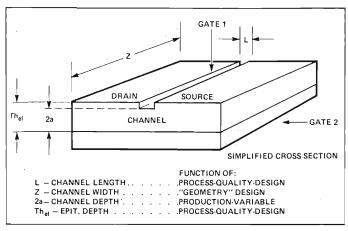

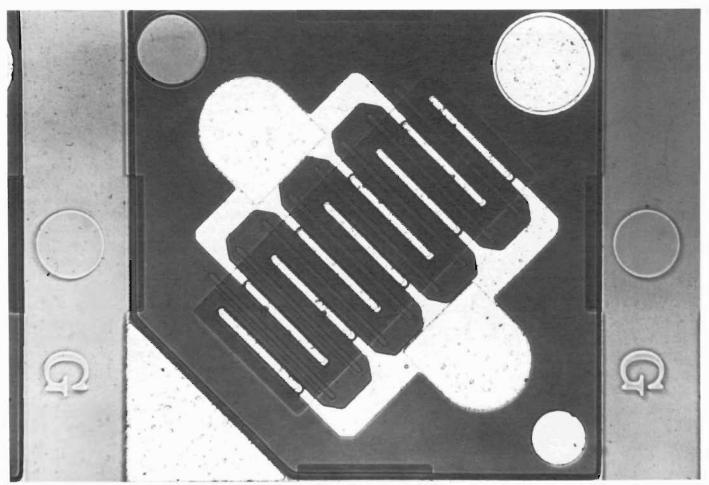

Figure 4 shows a cross section similar to that of a Teledyne 2N3436 N-channel. The bottom or "back" gate is uniform, while the top or "front" gate is a series of narrow diffused strips. The isolation region surrounding the device is a deep diffusion which meets both the back and front gates and thereby electrically connects them. The device is actually made up of several channels connected in parallel by a metallization pattern over the top oxide. Each channel has its own source and drain contact; the contacts are in series (source-drain-source-drain) with a front gate separating each one. Essentially, each contact is surrounded by the front gate-isolation gate combination. The design of a channel in the bulk of the semiconductor overcomes the difficulties met in using a channel which is restricted between a gate and the surface. In the latter case, surface effects such as ionization of adsorbed impurities result in low output impedance and noisy characteristics.

Simplified Cross Section of Teledyne 2N3436 Field Effect Fig.4, Transistor

There are two inherent properties of the FET that should be stressed here. One of the principal sources of noise in an injection transistor is the carrier recombination noise in the base. The FET is free of such noise because the current flow mechanism is determined by majority carriers (electrons in N-channels), just as in a metal conductor (typical noise figure, 1 dB). The other factor is radiation resistance. The transadmittance, gm, of the FET, is independent of the lifetime and will therefore be relatively insensitive to radiation damage.

#### **DESIGN PARAMETERS**

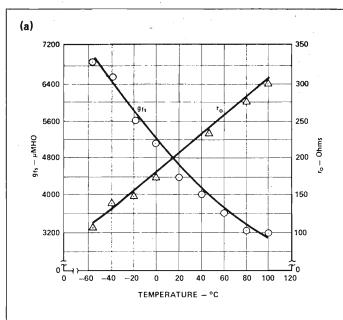

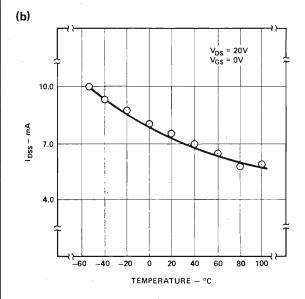

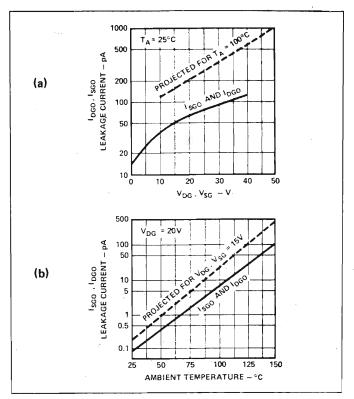

The following is a summary of some of the device parameters taken on a typical Teledyne 2N3436 unit. The variation with temperature of  $I_{\text{DSS}},\ r_{o},\ g_{fso},$  the source-to-gate leakage current  $I_{\text{SGO}}$  and the drain-to-gate leakage current  $I_{\text{DGO}},$  are shown in Fig. 5.

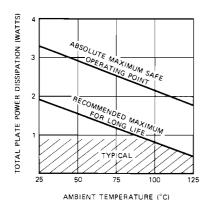

The transadmittance, Y<sub>fs</sub>, and saturation current, I<sub>DSS</sub>, of this device have a negative temperature coefficient between 0.5 and 0.6%/°C at room temperature and vary almost linearly between -55°C and +100°C. The compensation necessary for these variations is similar to the familiar schemes used for injection transistors and will be discussed briefly later. It is interesting to note the built-in protection in the FET against thermal runaway, as an increase in temperature reduces  $I_{\scriptsize DSS}$  and thereby the power generated in the device.

The variation in I<sub>DSS</sub> with temperature is a function of the change in material resistivity and in the change in channel thickness. The change in resistivity causes the  $I_{\text{DSS}}$  to decrease with an increase in temperature. The change in channel thickness is a result of the temperature coefficient of the depletion region and tends to open the channel up with an increase in temperature, thereby increasing IDSS. The total change is written as

$$\frac{\partial I_{DSS}}{\partial T} = Y_{fso} \ \frac{\partial |V_{GS(OFF)}|}{\partial T} - \frac{1}{p} \ \frac{\partial p}{\partial T} \ I_{DSS}.$$

There is a point at which  $\partial I_{DSS}/\partial T = 0$  given by

$$\frac{Y_{fso}}{I_{DSS}} = 3.2 \text{ volts}^{-1}$$

This can be extended to any bias point such that ID will remain constant with temperature for a constant V<sub>GS</sub> when the above condition is met.

$$I_{\text{D}} \simeq \frac{0.4~I_{\text{DSS}}}{V_{\text{GSIOFF12}}} \text{ or } V_{\text{GS}~z} \simeq (V_{\text{GSIOFF)}}) \text{ 0.64 V}$$

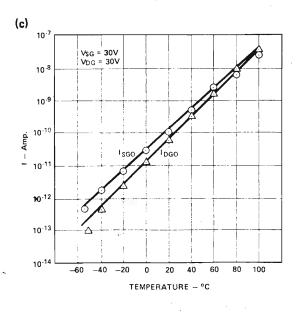

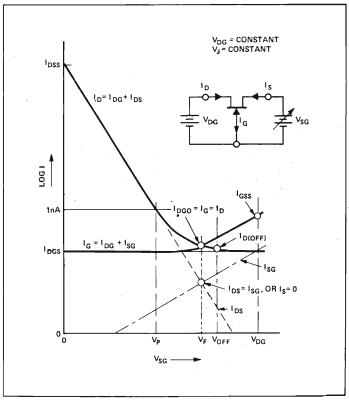

Both leakage currents  $I_{\text{SGO}}$  and  $I_{\text{DGO}}$  follow the theoretical dependence on temperature of diffused PN junctions in silicon, the small difference in leakage currents at the same

Fig. 5. Temperature Dependence of

- (a) Transconductance,  $Y_{fs}$  and "on" Resistance,  $r_{o}$ ;

- (b) Pinch Off Current, I<sub>DSS</sub>

(c) Source and Drain Leakage Currents, I<sub>SGO</sub> and I<sub>DGO</sub>

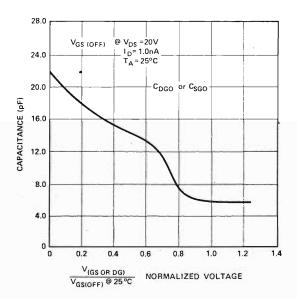

temperature being due to the geometry of the junctions. Another parameter which is of interest is the variation of gate to drain and gate to source capacitance as shown in Fig. 6.

In addition to a V-1/3 variation in capacitance above and below pinch off, we observe a rapid variation of capacitance with voltage at the pinch-off voltage. This is due to the fact that below pinch-off, the capacitance is that of the entire gate junction, whereas above pinch-off it is only the capacitance of the drain or the source isolated from each other.

Fig. 6. Variation of Source to Gate and Drain to Gate Capacitance with Normalized Bias

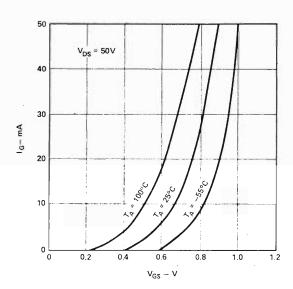

Fig. 7. Temperature Dependence of Forward Biased Gate Characteristics

In view of the possibility of allowing the gate to be positively biased with respect to the source, the plot of gate current vs. gate-to-source voltage is given in Fig. 7 for various temperatures. Except for gate current as shown, the device will operate in the normal way (i.e., no flow of current from drain to gate except for leakage current) so long as the drain voltage is not allowed to become more negative than the gate. This, of course, is a relatively simple

matter since the gate voltage cannot exceed that of a typical forward biased diode whereas the useful range of the device is at much higher drain voltages.

## APPLICATIONS OF FIELD EFFECT TRANSISTORS TO AMPLIFIERS

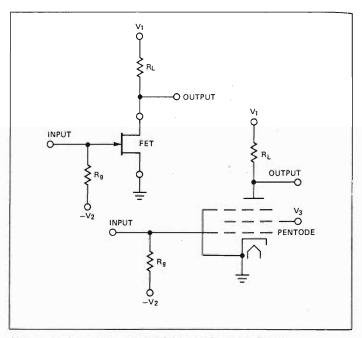

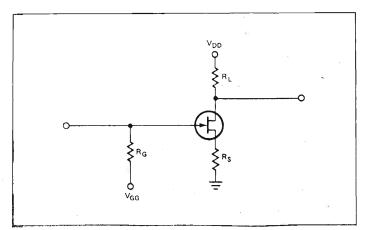

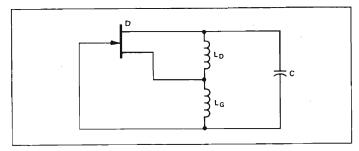

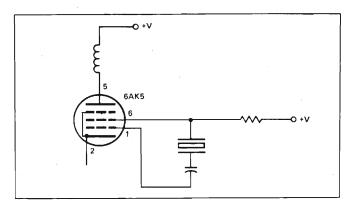

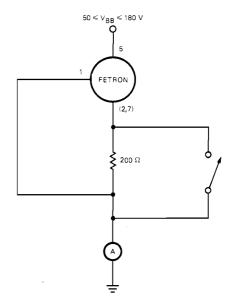

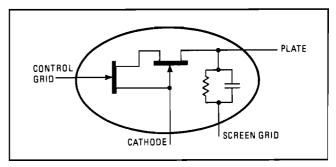

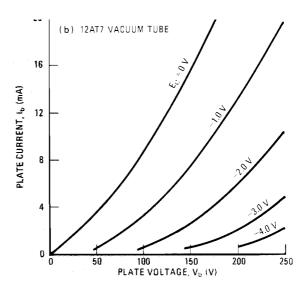

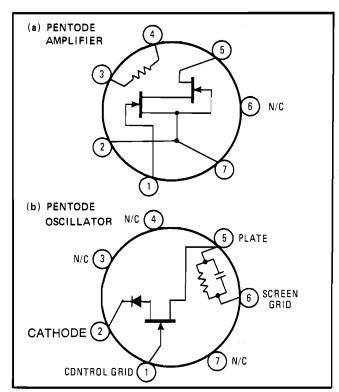

Figure 8 shows the biasing of a field effect transistor as well as of a vacuum tube pentode to illustrate the analogy. The biasing may vary widely with the application, the most common being the grounded source configuration as shown.

Fig. 8. Analogy Between an FET and a Pentode Circuit

The expression for the gain of such an amplifier is

$$A_{V} = \frac{\mu R_{L}}{r_{ds} + R_{L}} = \frac{Y_{fs} r_{ds} R_{L}}{r_{ds} + R_{L}} = \frac{Y_{fs} R_{L}}{1 + R_{L} g_{os}}$$

where

$$\mu = Y_{fs} r_{ds}$$

.

If  $r_{ds} >> R_L$  the expression for voltage gain reduces to:  $A_V = Y_{fs} R_L \text{ at low frequencies.}$

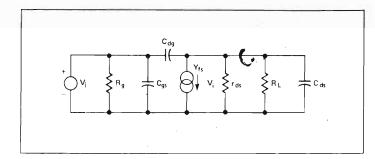

Fig. 9. Small Signal Equivalent Circuit of an FET

The small signal equivalent circuit is shown in Fig. 9. Because of the variation of  $Y_{\rm fs}$  with  $V_{\rm GS}$ , the requirement for maximum gain indicates the desirability to operate close to  $V_{\rm GS}=0$ . This brings up the question of the possibility of biasing the gate in such a way that the latter is at ground potential in the quiescent state. Such an operation is possible since a forward biased gate junction does not conduct appreciable current (thereby reducing the input impedance

drastically) until a positive voltage of about 0.3 volts is reached. Depending on the amplification and signal levels at any given gate input, the DC bias may be picked slightly negative with respect to the source.

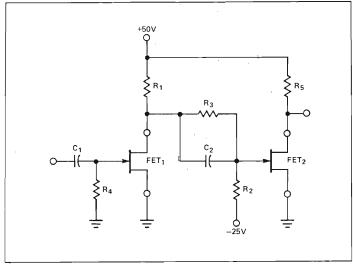

Figure 10 shows a simple circuit for an AC amplifier designed for a gain of  $2 \times 10^3$ .

We will assume that FET<sub>1</sub> and FET<sub>2</sub> are identical with  $V_{GS(OFF)}=-2.0$  volts,  $I_{DSS}=3$  mA,  $Y_{fso}=4000~\mu mhos$  and  $g_{os}=10~\mu mhos$ . This circuit will be designed so that the gate of FET<sub>1</sub> is at ground ( $V_{GS1}=0$ ) and the gate of FET<sub>2</sub> is at -1 volt ( $V_{GS2}=-1$  V). For a gain of 40 for the first stage, the load at the drain must be 11.1 k and this can be calculated as

$$\begin{split} R_{L} &= \frac{A_{V}}{Y_{fs} - A_{V}g_{os}} = \frac{40}{(4000\text{-}400)\ 10^{-6}} \\ &= \frac{R_{L} \times R_{2}}{R_{L} + R_{2}} \\ &= 11.1\ k\ (assuming\ X_{CL} << R_{L} + R_{2}). \end{split}$$

Fig. 10. FET Amplifier Circuit

At steady-state,  $I_{D_1}=3$  mA, and  $V_{GS2}=-1$  V. Therefore, if  $R_2$  and  $R_3$  are much greater than  $R_1$ , then  $R_1=11,000$  ohms. Furthermore, since the DC loading of  $R_2$  and  $R_3$  can then be neglected,  $V_{DS1}=17$  volts and

$$\frac{R_3 \times 42}{R_3 + R_2} = 18.$$

Letting  $R_2$  be 1 Meg gives a value for  $R_3$  of approximately 0.75 Meg. The value of  $R_5$  can now be determined from the overall gain of 2 x 10 $^3$ . Therefore,  $Y_{\rm fs2}R_5$  must equal 2 x 10 $^3$ / 40 or 50. But  $Y_{\rm fs2}$  is

$$Y_{fs2} = Y_{fs0} \left( 1 - \frac{V_{GS}}{V_{GS(OFF)}} \right) = 4000 (1 - 0.5)$$

= 2000 \( \mu \text{mhos}

giving a minimum value for  $R_{\rm s}$  of 33,000 ohms. It will be noted that  $R_{\rm s}$  can be made larger to obtain still higher gain, the choice being determined by the maximum voltage swing desired at the output and the harmonic distortion that can be tolerated. However, the advantages of using a high voltage device to achieve higher gains are readily apparent.

For maximum voltage gain at the same power level, the usable voltage gain is that region of the device between the gate cutoff voltage  $V_{\text{GS(OFF)}}$  and the maximum supply voltage.  $V_i$ . This indicates a figure of merit (g  $_{\text{a}}V_{\text{A}}$ )/I, where  $V_{\text{A}}$  is the available voltage swing or  $V_{\text{GS(OFF)}}$ . Since the

maximum load resistance that can be used is  $V_{\text{A}}/I_{\text{DSS}}$ , the maximum gain available is

$$\frac{Y_{fs}}{g_{os} + I_{DSS}}$$

(This number might be typically 100). This figure of merit is especially interesting from two points of view: 1) A unit having a large  $Y_{\rm fs}$  and  $V_{\rm A}$ , as shown in this example, and a low  $I_{\rm DSS}$  and  $g_{\rm os}$ , can be used in almost any present day electronic application where voltage gain and power gain are a prerequisite, so that the larger this number is, the greater the advantages and flexibility. 2) Even though FET units have been made in the past with rather large transadmittance (50 to 100 mmhos) their scope in practical circuits has been limited because of either a small  $V_{\rm A}$  or large  $I_{\rm DSS}$  or both. Such units have been limited to applications that can tolerate a voltage gain less than unity.

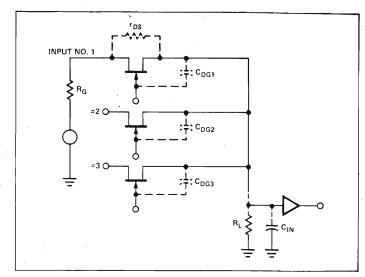

In small signal applications, the frequency limitation of this device is determined by the Miller capacitance as shown in the equivalent circuit given in Fig. 9. There is no other practical frequency limitation because the field effect is a majority carrier device in contrast with the injection transistor which is a minority carrier device.

Referring to Fig. 9, we see that the input impedance will decrease with increasing frequencies at which the quantity  $1/2\pi C_{is}$  becomes comparable to the input resistance. Furthermore, the gain bandwidth product will be approximately:

Gain bandwidth =

$$\frac{Y_{fs}}{2\pi C_{is}}$$

This dictates a direct compromise between circuit gain and bandwidth as is well known in network theory. Since  $Y_{fs}$  and  $C_{is}$  both decrease with increasing bias voltage,  $V_{GS}$ , it is interesting to investigate the effect on gain-bandwidth figure of merit. As  $V_{GS}$  is increased (more negative for N channel), the gain-bandwidth product has a slight peak at about 15% of gate cutoff voltage,  $V_{GS(OFF)}$ . However, the product-is essentially constant for values of  $V_{GS}$  less than about 30% of  $V_{GS(OFF)}$ .

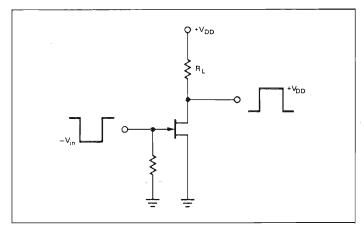

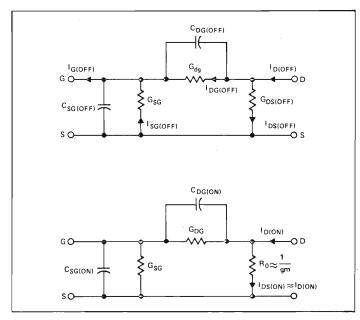

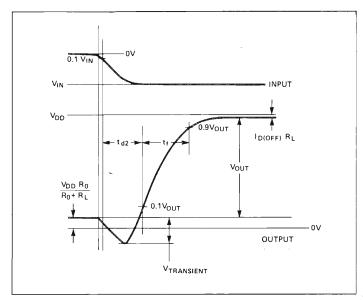

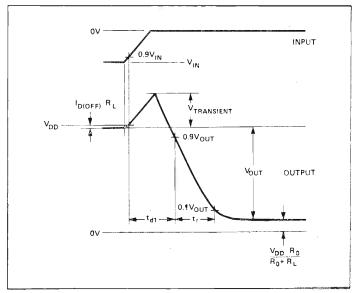

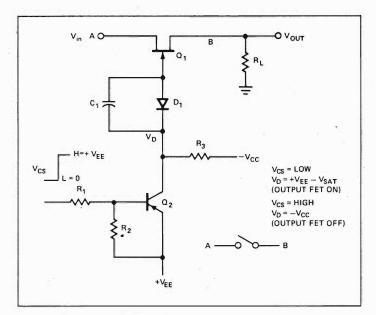

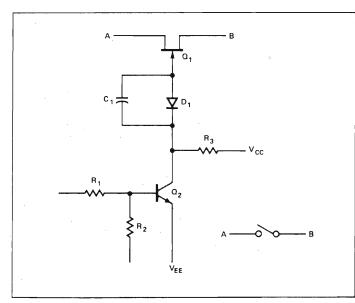

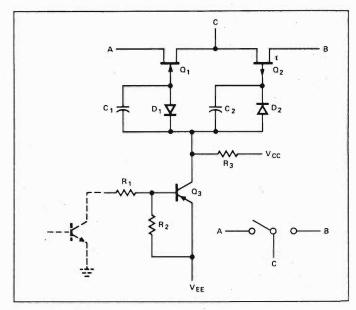

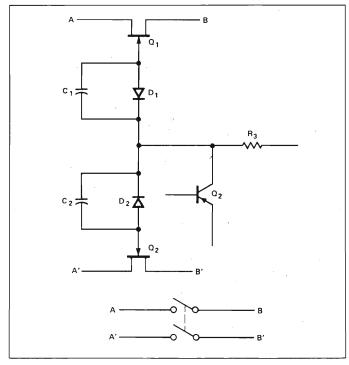

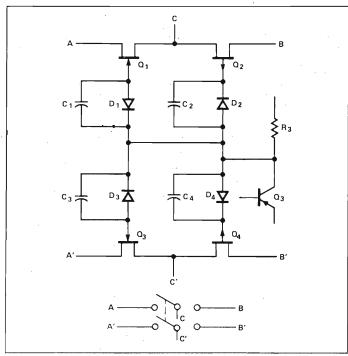

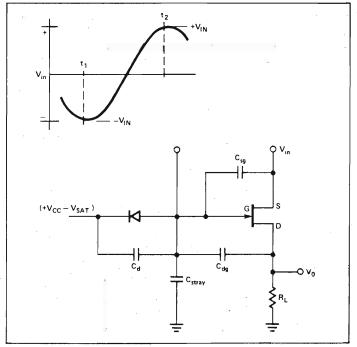

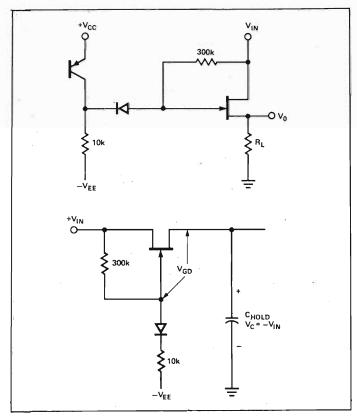

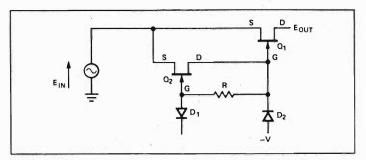

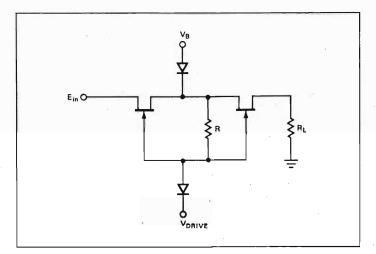

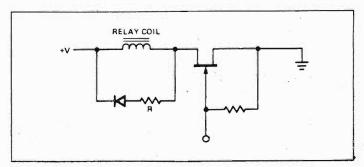

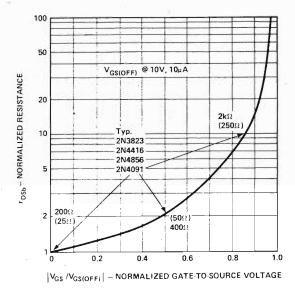

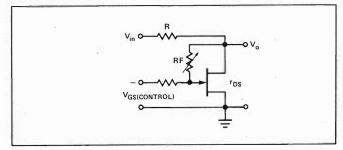

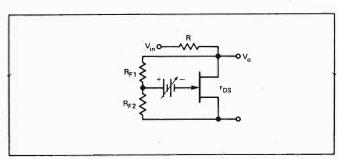

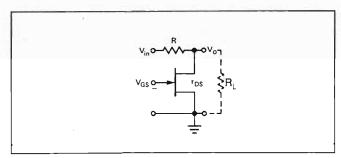

#### **SWITCHING APPLICATIONS**

These applications refer to the case where, in analogy to the injection type transistor, the device is either "on" or "off." The parameters of interest here are the transadmittance, the "off" current and the "on" impedance,  $r_{ds}$ . The "off" current is the drain current when the unit is biased beyond pinch-off and is of the order of the leakage currents. The "on" impedance,  $r_{ds}$  is the slope of the curves in Fig. 3 in the region between  $V_{\text{D}} = 0$  and  $V_{\text{D}} = V_{\text{GS(OFF)}}$

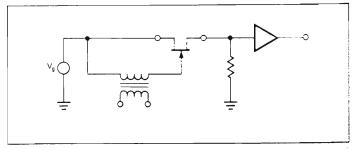

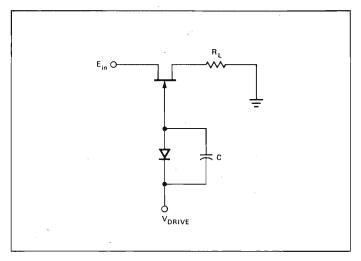

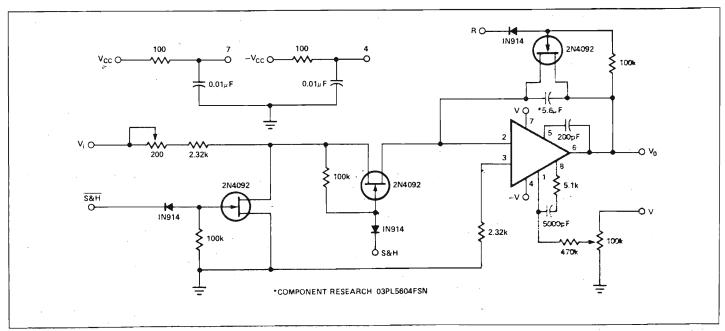

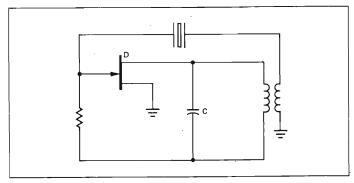

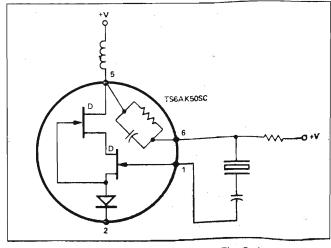

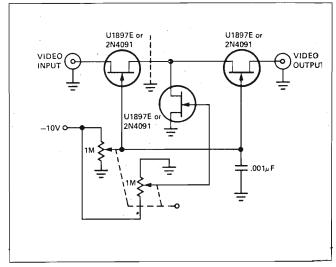

Fig. 11. FET Chopper Circuit

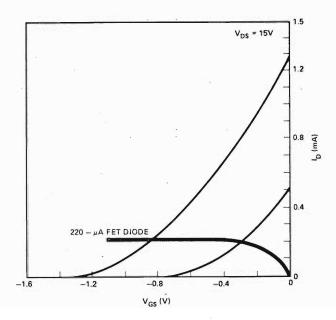

There are switching applications such as in choppers where the field effect transistor is very much superior to the conventional transistor. When used in an unbalanced

configuration as in Fig. 11, the offset voltage when the unit is turned off would be of the order of 200 microvolts or at least one hundredth of the offset voltage that would result if an injection type transistor were used.

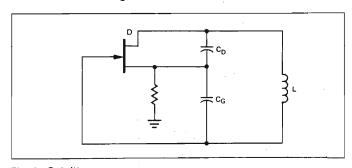

In the latter case, the offset voltage is primarily a function of the transport factor of the transistor and is therefore fairly high. It might be of the order of 50 mV in the normal and 5 mV in the inverse configuration at zero load current, whereas this voltage is zero in the FET because the drain to source characteristics start right at the origin. The offset voltage at zero load current would therefore be zero. The offset voltage when the unit is shut off is determined (as quoted) by the leakage current and the load impedance as in conventional injection type transistors. If one were to use matched pairs to cancel the offset due to the leakage currents, this improvement in addition to the true zero offset in the "on" condition makes the FET chopper applicable in low level circuits where mechanical relays have had to be used in the past. Junction capacitance is important in switching circuits since it limits the turn-on and turn-off times when switching into a given load resistance, R<sub>L</sub>. The "on" resistance of the FET is also important in switching circuits since it determines the size of the load resistance and therefore the switching time.

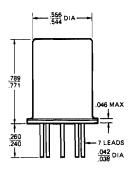

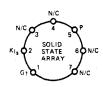

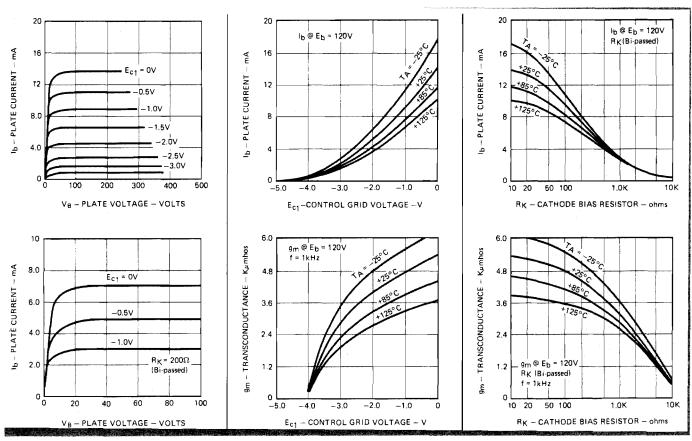

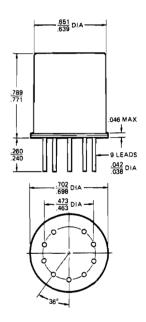

#### **GENERAL CHARACTERISTICS**

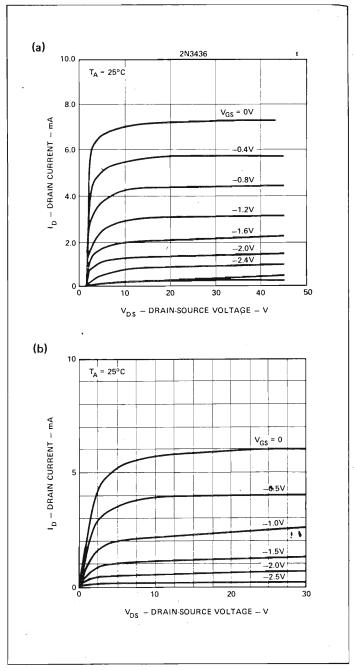

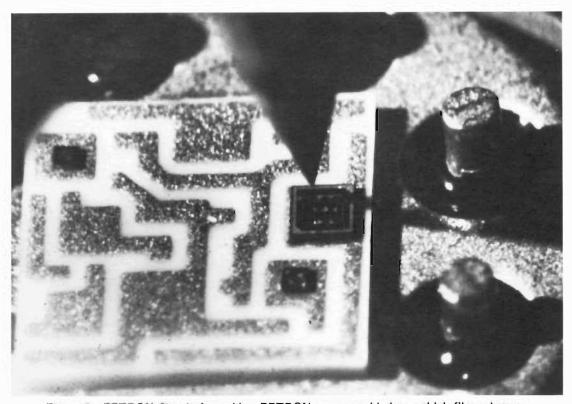

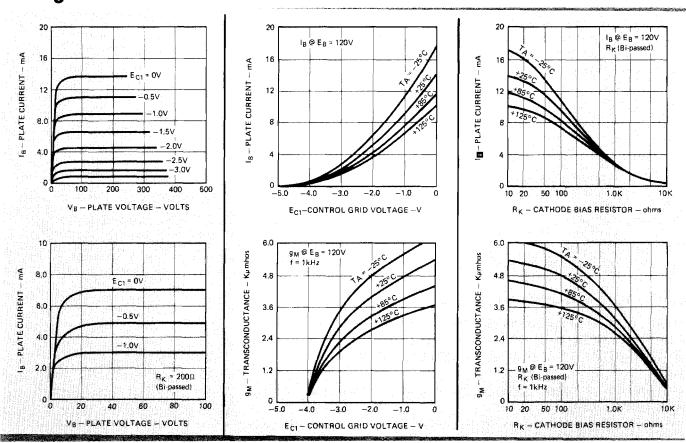

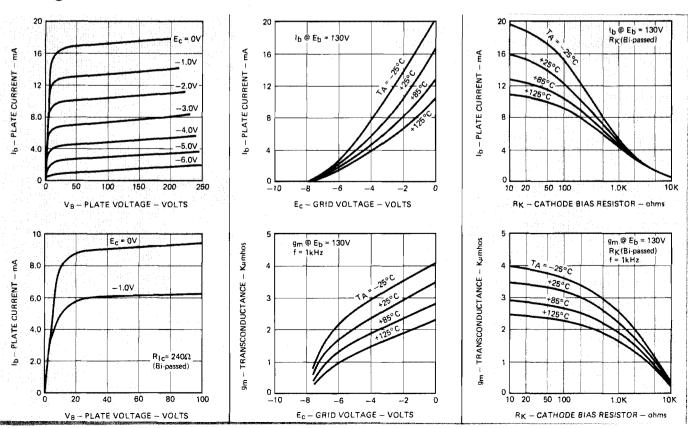

Shown in Fig. 12 are the specifications for the Teledyne 2N3436 and 2N3967 field effect transistors. These specifications may be referred to when studying the curves that follow to get an indication of the actual range of the parameters.

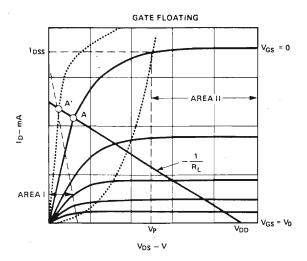

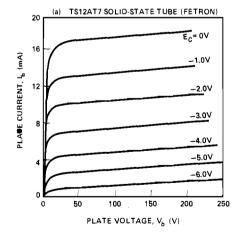

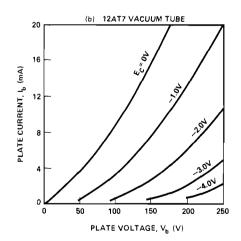

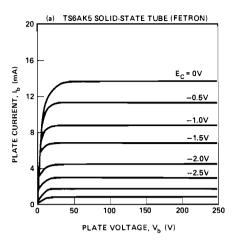

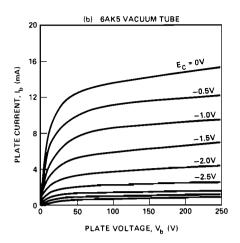

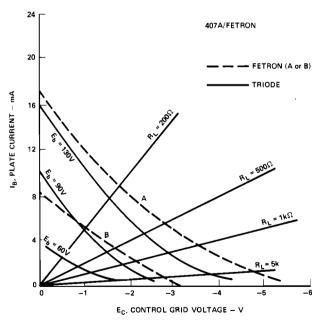

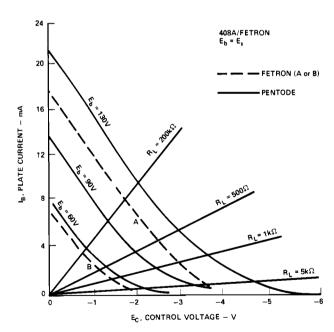

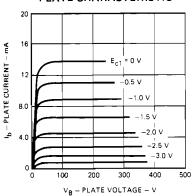

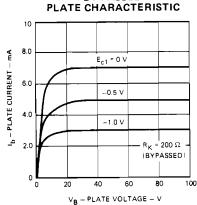

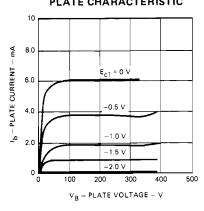

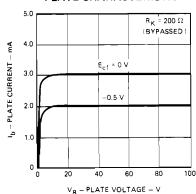

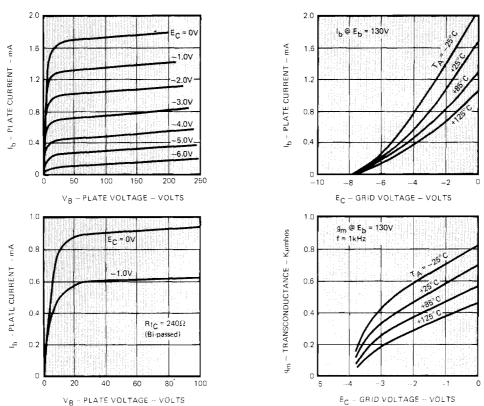

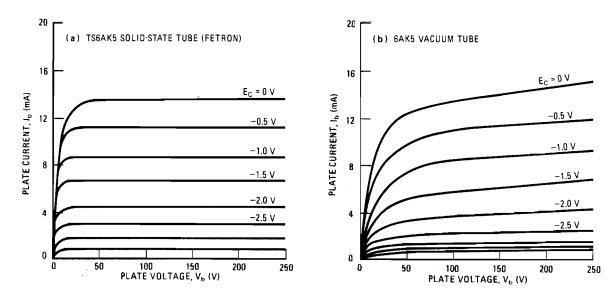

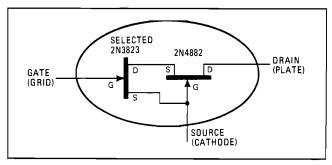

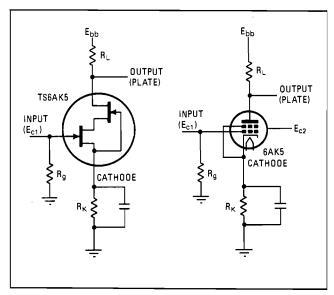

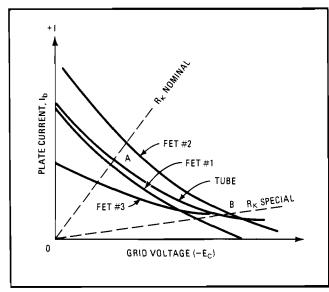

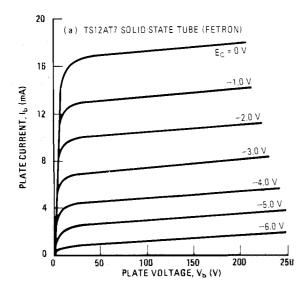

Typical drain current families are shown in Figs. 13a and 13b. These curves are of limited use in circuit design (as are the grounded emitter collector current families for injection transistors), but are included to show their similarity to vacuum pentode characteristics.

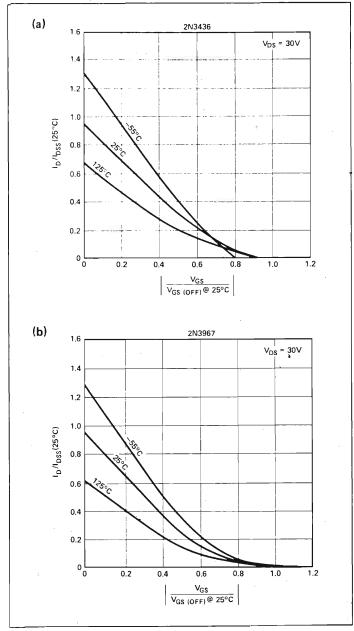

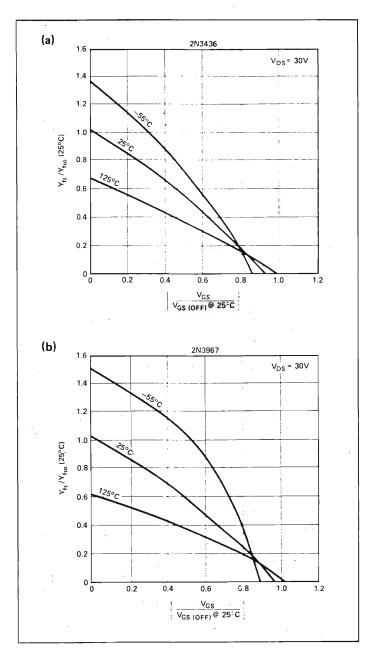

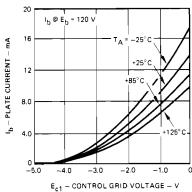

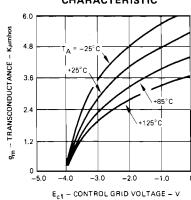

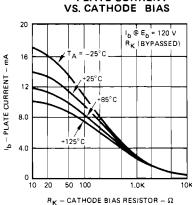

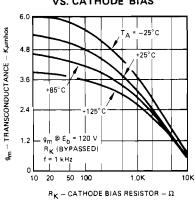

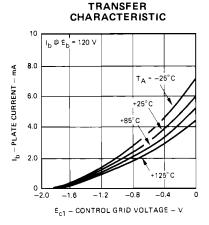

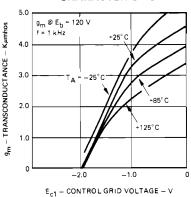

Figures 14a, 14b, 15a and 15b show the temperature dependence of drain current,  $I_D$  and transadmittance,  $Y_{fs}$ , as a function of gate to source voltage,  $V_{GS}$ . These characteristics are normalized and their usefulness in circuit design will be shown in examples given in a later section.

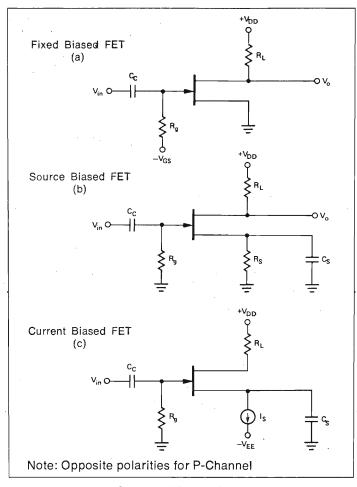

#### DC BIAS CONSIDERATIONS

In this section we consider the problem of biasing a grounded source amplifier stage at a particular operating point and maintaining the operating point within specified limits as the temperature varies or as different devices are placed in the circuit. Three circuits will be considered: 1) A grounded source amplifier without feedback, 2) an ampli-

Fig. 13. Typical Field Effect Drain Current Families

fier with source degeneration, and 3) an amplifier with drain to gate feedback.

|                          | Characteristic                     | 2N3436 |        |            |                                                 | 2N3967 |      |                |                                                 |

|--------------------------|------------------------------------|--------|--------|------------|-------------------------------------------------|--------|------|----------------|-------------------------------------------------|

| Symbol                   |                                    | Min.   | Max.   | Units      | Test Conditions                                 | Min.   | Max. | Units          | Test Conditions                                 |

| BV <sub>DGO</sub>        | Drain to gate breakdown<br>Voltage | 50     |        | Volts      | $I_D = 1.0 \ \mu A, \ I_S = 0$                  | 30     |      | Volts          | $I_0 = 1.0 \ \mu A, \ I_S = 0$                  |

| I <sub>ess</sub>         | Total gate leakage current         |        | 0.5    | nA         | $V_{DG} = 30 \text{ V}, V_{DS} = 0$             | 1      | 0.1  | nA             | $V_{DG} = 20 \text{ V}, V_{DS} = 0$             |

| I <sub>GSS</sub> (150°C) | Total gate leakage current         |        | 1.0    | μ <b>Α</b> | $V_{DG} = 30 \text{ V}, V_{DS} = 0$             |        | 0.2  | $\mu A$        | $V_{DG} = 20 \text{ V}, V_{CS} = 0$             |

| I <sub>DSS</sub>         | Saturation current                 | 3.0    | 15     | mA         | $V_{DS} = 30 \text{ V}, V_{GS} = 0$             | 2.5    | 10   | mA             | $V_{DS} = 20 \text{ V}, V_{GS} = 0$             |

| Y <sub>fs</sub>          | Transadmittance                    | 2500   | 10,000 | $\mu$ mhos | $V_{DS} = 30 \text{ V}, V_{GS} = 0$             | 1600   | 2400 | μ <b>m</b> hos | $V_{DS} = 20 \text{ V}, I_D = I_{\pi \Lambda}$  |

| V <sub>GS(OFF)</sub>     | Gate cutoff voltage                |        | 10.0   | Volts      | $V_{DS} = 20 \text{ V}, I_{D} = 1.0 \text{ nA}$ |        | 5.0  | Volts          | $V_{DS} = 20 \text{ V}, I_{D} = 1.0 \text{ nA}$ |

| C <sub>dg</sub>          | Drain to gate capacitance          | 8      | 5.0    | рF         | $V_{DG} = 10 \text{ V}, I_S = 0$                | -      | 1.3  | рF             | $V_{0G} = 10 \text{ V}, I_S = 0$                |

| C <sup>sg</sup>          | Source to gate capacitance         |        | 5.0    | р <b>F</b> | $V_{SG} = 10 \text{ V}, I_{D} = 0$              |        | 1.5  | pF             | $V_{SG} = 10 \text{ V}, I_0 = 0$                |

Fig. 12.

Fig. 14. Normalized Transfer Characteristics

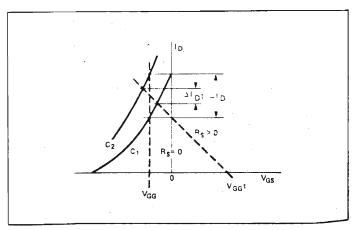

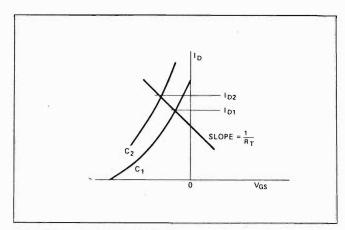

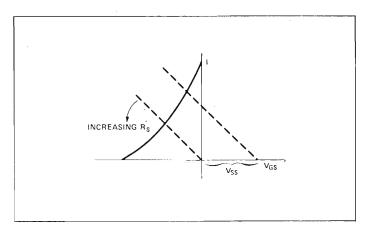

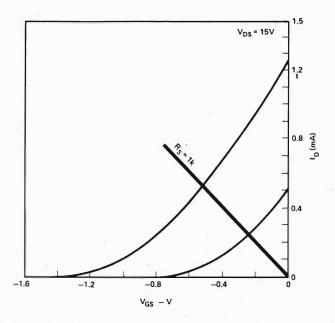

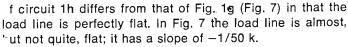

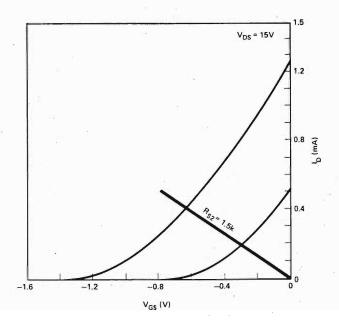

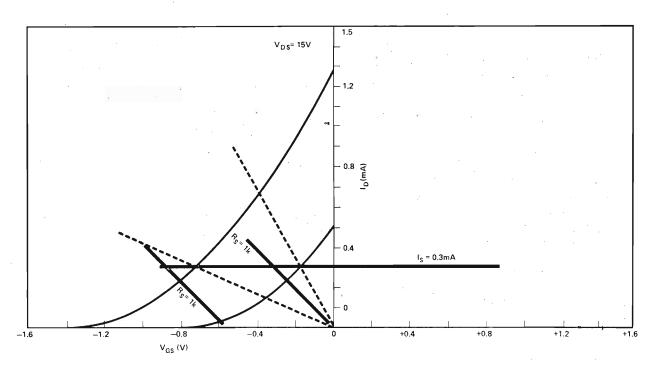

Shown in Fig. 16 is a grounded source amplifier. The TET transfer characteristics representing extremes with espect to temperature and devices are shown in Fig. 17 by the curves  $C_1$  and  $C_2$ . Consider first the case with  $R_S=0$

Fig. 16. Grounded Source FET Amplifier

Fig. 15. Normalized Transconductance vs. Gate to Source Voltage

(no degeneration) and a bias voltage  $V_{\text{GG}}$ . The change in drain current  $\Delta I_D$  will take place along the  $R_S=0$  load line as indicated in the figure. It can be seen that the amount of this change can be quite severe in many applications.

Fig. 17. Transfer Characteristics

For the case of  $R_s>0$  (source degeneration) with the same initial operating point, the  $R_s$  load line will be as shown in Fig. 16. The bias voltage for this condition is now  $V_{\text{GG}}{}'.$  The change in drain current  $\Delta l'_{\text{D}}$  occurs along the  $R_s>0$  load line and is reduced over the  $R_s=0$  case by the amount indicated. Theoretically, we can make  $R_s$  as large as we please to minimize the shift in the operating point with temperature and with different devices in the circuit. The practical limit on the size of the  $R_s$  is determined by the bias voltage available and by the required low frequency gain. The low frequency voltage gain with source degeneration is

$$A_V = \left[ \frac{Y_{I_s} R_L}{1 + Y_{I_s} R_S + g_{ns} (R_L + R_S)} \right]$$

where

Y<sub>fs</sub> is the transadmittance at the operating point

gos is the output conductance at the operating point

$$A_{v} \approx \frac{Y_{f_{s}}R_{L}}{1 + Y_{f_{s}}R_{S}} \approx \frac{R_{\cdot}}{R_{s}} \text{ for } Y_{f_{s}}R_{S} >> 1$$

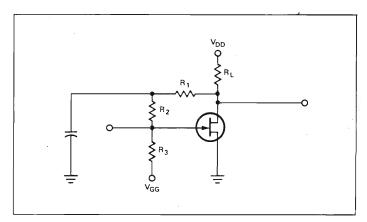

An amplifier with drain to gate feedback is shown in Fig. 18. Assume that the direct current flowing through  $R_{\scriptscriptstyle 1},~R_{\scriptscriptstyle 2}$  and  $R_{\scriptscriptstyle 3}$  is much smaller than the current  $I_{\scriptscriptstyle L}$  flowing through  $R_{\scriptscriptstyle L}.$  Also, we will neglect the junction leakage currents. Then

$$I_\text{D} \simeq I_\text{L}$$

Fig. 18. Grounded Source Amplifier with Drain to Gate Feedback

Now consider a small change in the drain current. Then

$$\Delta V_{GS} \simeq \frac{R_3 R_L}{R_1 + R_2 + R_3} \; \Delta I_D. \label{eq:deltaVGS}$$

Let

$$R_{T} = \frac{R_{3}R_{L}}{R_{1} + R_{2} + R_{3}}$$

Ther

$$\frac{\Delta I_{\text{D}}}{\Delta V_{\text{GS}}} \simeq \frac{1}{R_{\text{I}}}$$

The transfer characteristics' extremes shown previously are again shown in Fig. 19. As an example, let us assume that the maximum allowable shift in drain current is as shown in the figure. The R- must be equal to or greater than the reciprocal of the slope of the line connecting the two points of intersection of the maximum and minimum drain currents and the transfer characteristics.

In the preceding discussion on biasing considerations we have used the regular characteristics rather than the normalized characteristics for the sake of clarity. The normalized characteristics can, of course, be used if the load lines are properly normalized to

$$\frac{V_{\text{GS/OFF}}(25^{\circ}\text{C})}{I_{\text{DSS}}(25^{\circ}\text{C})}$$

Fig. 19. Transfer Characteristics

for the particular devices used. We have also neglected the change in drain current with the change in drain to source voltage. This change, however, is small compared to the change due to temperature and the normal variation in drain current characteristics from one device to another

The three biasing methods shown are the basic methods used in vacuum tube and transistor circuit design. Where greater operating point stability is required, more elaborate forms of biasing and compensating will have to be employed.

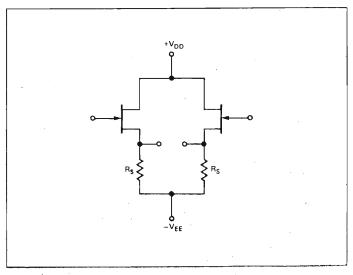

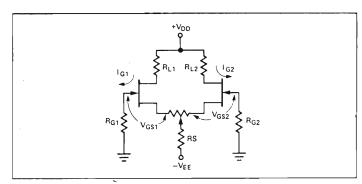

#### **APPLICATION OF PAIRS**

In this section, two examples of FET amplifier circuits are given to show how FET pairs can be used to some advantage. The examples given are in simple form, but can be extended and applied in more complex configurations as specified applications are considered.

The voltage gain of the circuit shown in Fig. 16 was given as

$$A_V = \left[ \frac{Y_{f_S} R_L}{1 + Y_{f_S} R_S + g_{o_S} (R_S + R_L)} \right] \label{eq:AV}$$

The gain for a given FET amplifier is limited by the size of  $R_{\text{\tiny L}}$ . However, to insure operation in the pinch-off region where the gain is a maximum,

$$R_{L} < \frac{V_{DD} - |V_{GS(OFF)}|}{I_{D}}$$

Fig. 20. A Two FET Amplifier

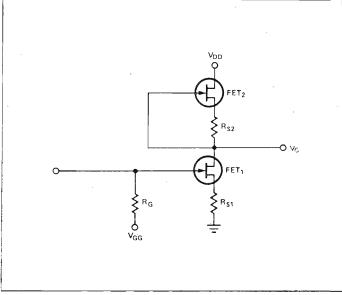

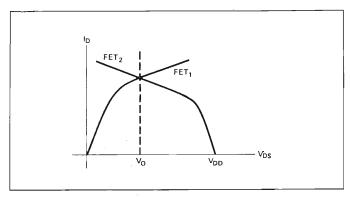

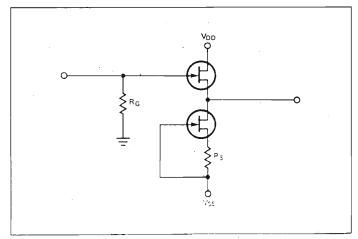

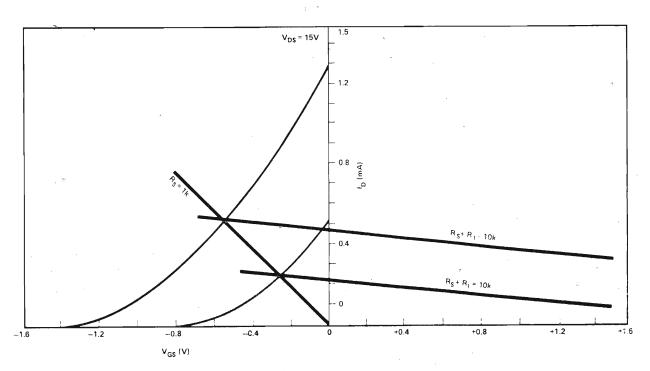

Figure 20 shows a two FET amplifier designed to give maximum voltage gain with a limited supply voltage  $V_{\text{DD}}$ , and some temperature stability. Here the load resistance has been replaced by another FET. The operation of this circuit is best shown by the grounded source characteristics in Fig. 21. The load is now effectively the drain resistance of the upper FET,  $1/g_{os2}$ . The gain for this configuration is

$$\begin{split} A_{v} &= \frac{Y_{f_{51}}}{g_{os1} + g_{os2} + R_{S1} \left(Y_{f_{51}} g_{os2} + g_{os1} g_{os2}\right)} \\ &\approx \frac{1}{R_{S1} g_{os2}} \end{split}$$

21. Two FET Amplifier Characteristics

This circuit has the advantage of improved operating point stability if the drain currents of both FET's have approximately equal temperature co-efficients. For best operation, the characteristics of the two devices (in particular,  $I_{DSS}$  and  $V_{P}$ ) should be closely matched.

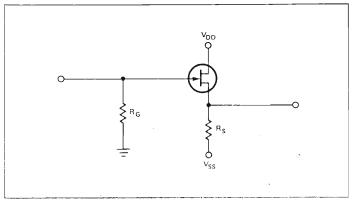

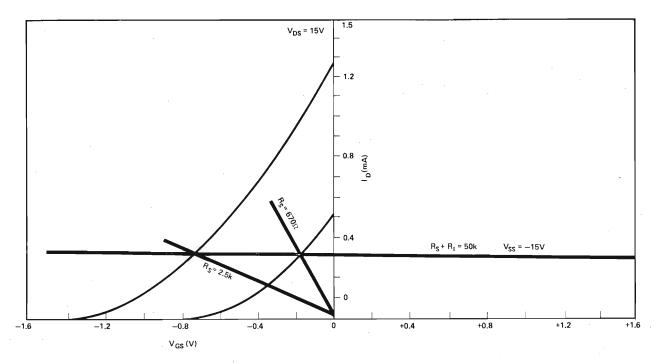

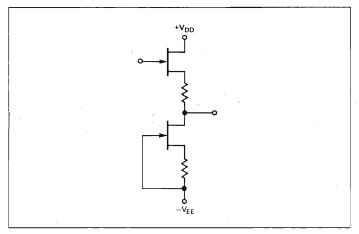

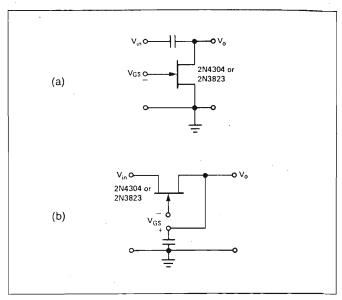

Field effect source followers can be used in the same manner as vacuum tube cathode followers and transistor emitter followers. A typical source follower circuit is shown in Fig. 22. Shown in Fig. 23 is the transfer characteristics for the FET. Consider the case of  $V_{\text{SS}}=0$ . The voltage gain of the source follower is

$$A_{v} = \frac{Y_{fs}R_{\S}}{1+R_{S}\left(Y_{fs}+g_{os}\right)} \approx \frac{Y_{fs}R_{S}}{1+Y_{fs}R_{S}}$$

Fig. 22. FET Source Follower

To approach unity gain,  $Y_{13}R_{5}$  must be much greater than one. We can make  $R_{5}$  large, but as we increase  $R_{5}$ , the operating point moves down the transfer characteristics to the region where  $Y_{13}$  is low (refer to Figs. 15a and 15b,  $Y_{13}$  vs.  $V_{23}$ ). Therefore, for  $V_{23}=0$  the voltage gain is much less than unity. By making  $V_{33}$  negative, the  $R_{5}$  load line is

Fig. 23. Transfer Characteristics

translated to the right as indicated in Fig. 23. The voltage gain is increased since the operating point is moved up the transfer characteristics where the  $Y_{\ell_s}$  is higher, thus increasing  $Y_{\ell_s}R_s$ .

Shown in Fig. 24 is a two FET source follower. Here we have replaced the load resistor with a field effect constant current load. The operating point of the upper FET is determined by the drain current of the lower FET. This configuration requires that the I<sub>DSS</sub> of the upper FET must be less than that of the lower. The output impedance of this circuit is approximately 1/Y<sub>122</sub>. This circuit also has the advantage of improved operating point stability since the drain currents of both FET's vary with temperature in a similar manner.

Fig. 24. Two FET Source Follower

## NOISE CHARACTERISTICS OF FIELD EFFECT TRANSISTORS

The fundamental limitation of the sensitivity of any network is set by the amount of noise generated by that network. Noise, irrespective of the source or mechanism of its generation, has the dimensions of power (i.e.,  $P_n = KTB$ ) and is characterized by its random or uncorrelated behavior with time. When the signal power fed into the input of an active network is decreased beyond a certain level, the signal at the output of the network is no longer recognizable in the noise generated within the network.

The generation of noise is associated with all physical devices whether active or passive. Field effect transistors (FET) like all devices are subject to a physical environment and exhibit several types of noise. The difference is that,

under some operating conditions, FET's exhibit noise behavior superior to transistors and vacuum tubes.

In applications requiring low noise amplification below 500 Hz, the low noise characteristics of the Teledyne FET are particularly suitable because of its low I/f noise. The FET has many of the better features of the vacuum tube such as high input impedance and transadmittance without the higher I/f noise, does not require a high plate voltage or a filament supply, and the FET is not microphonic.

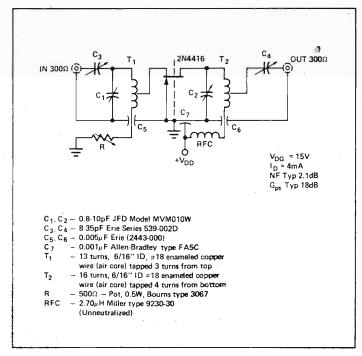

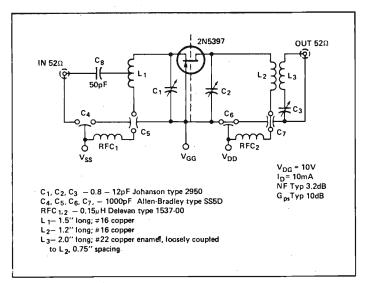

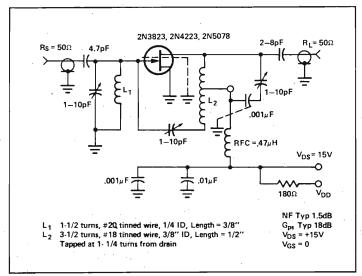

Popular junction FET's for varying application — N-channel unless otherwise noted.

- 1. High Voltage (guaranteed  $BV_{DGO}$  greater than 150 to 300 V) 2N4881-6; AN5277-8.

- 2. Low Noise (low en guaranteed) 2N5391-6.

- 3. Switching (guaranteed r<sub>ds</sub> less than 5-100 ohms)

- 2N3970-72; 2N4091-3; 2N4391-3; 2N5432-4; 2N4856-{ 2N4977-9; 2N5018-9 (P-channel); P1086-7E (P-channel U1897-9E (N-channel).

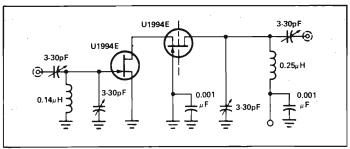

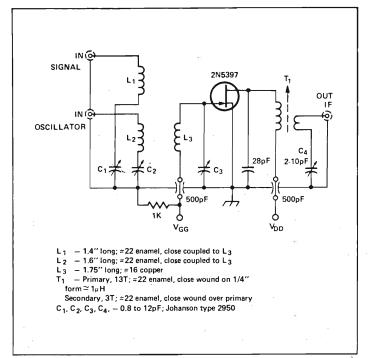

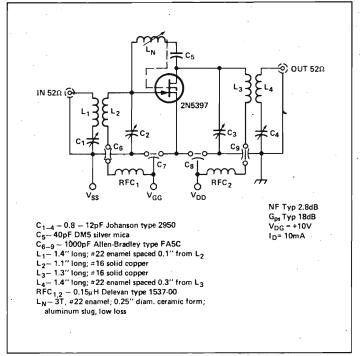

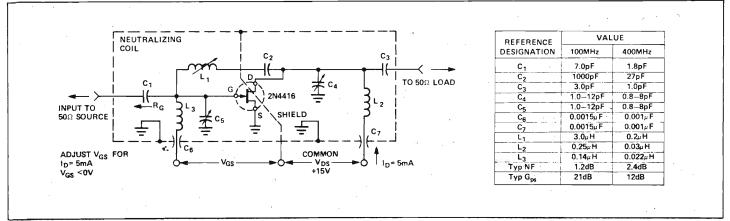

- High Frequency Amplifier and Mixers (200-500 M) operation) 2N4416; 2N3823; 2N4223; 2N5078; U1994 U2047E, U1837E.

- Low Leakage Amplifiers (less than 1-5 pA input ct rent) 2N5647-9; U1714.

- General Purpose N-Channel Amplifiers, 2N3436-2N3821-3; 2N3966-9; 2N4220-4; 2N4302-4 (Epoxy).

- 7. General Purpose P-Channel Amplifiers 2N2606-9.

- Dual Matched FET's 2N5045-7; SU2365-9. A 2N5196-2N3954-6; 2N3921-2; 2N4084-5; 2N3934-5; 2N4082-TD5902-9.

## Junction FET Analogies and Parameter Tradeoffs

Quite frequently, a specification will be written combining the best of several different devices into one that, with present technology, is impossible to manufacture. All that is usually lost here is valuable time and a lot of wasted effort. Other times, a specification reflects a 2-3% yield item which was not the intent in the first place. This misunderstanding becomes costly via the "Cadillac" price on a required "Volkswagen" item.

It is not necessary to know every little theoretical detail of the device physics and design equations involved in JFETs, but a logical concept of parameter interactions and tradeoffs will help in making parameter selections and combining device specs.

#### **JFET Analogies**

For those not familiar with FET analogies and tradeoffs, the following discussion gives the beginner a working knowledge based on logic for FET characteristics.

For a working model, let's consider a common garden hose, its characteristics, interactions, and tradeoffs. Essentially the same problems arise in designing and selecting FETs.

- 1.  $I_{DSS}$  (Drain Saturation Current) All JFETs are depletion mode type normally "on" when no bias is applied.  $I_{DSS}$  is similar to the measurement of gallons/hr. flow through the hose. Up to a point,  $I_{DSS}$  increases with increasing voltage, just as water flow increases with line pressure, then the flow limits.

- 2.  $V_{\text{GS}(\text{OFF})}$  (Gate-Source Cutoff Voltage) the required bias voltage to shut off the FET is like measuring how far the faucet valve needs to be shut, to stop the flow. Interestingly it is essentially independent of applied pressure (voltage).

- 3.  $Y_{FS}$  (Forward transadmittance) By definition, it is the quantity change in drain current for the quantity change in gate-source voltage,  $Y_{fe} = \frac{\Delta I_D}{\Delta V_{GS}} |V_{DS} = K$ , or a ratio of change of water flow in relation to a defined change in faucet opening.

#### 4. IDSS, VGS(off), YFS Interactions

For a JFET, an interaction exists between the three key 21<sub>DSS</sub>

parameters, namely  $Y_{\text{FS}} \, \stackrel{\bullet}{=} \, \stackrel{- \cdot \cup 33}{V_{\text{GS(off)}}}.$  As the garden hose

inside diameter increases, more water can flow per hou  $(I_{DSS})$ , but also the greater distance the full size non restricting hose faucet would have to be shut off  $V_{GS(eff)}$  Similarly, the greater change in water flow for a giver faucet adjustment  $(Y_{FS})$ . i.e. Fire hydrant and hose ver sus  $\frac{34}{7}$  faucet and hose.

5. **V**<sub>(BR)GSS</sub> — Gate-Source Breakdown Voltage This is the maximum source &/or drain junction operating voltage. How many PSI the hose will handle before it breaks.

#### 6. I<sub>G</sub>, I<sub>GSS</sub> — Gate Leakage Current

A measure of how perfect the junction is. The amount of water leakage at the valve connection or pin holes along the hose.

#### 7. Yos — Output Admittance

A measure of the inverse of the slope of the drain current as the Drain-Gate voltage is increased. Small because, like the hose, beyond a certain line pressure little extra water flows for a further increase in pressure.

#### 8. r<sub>DS</sub> — Drain "ON" resistance

A measure of the non-biased channel "ON" resistance.

Simply is the familiar  $r_{DS}=\frac{pL}{A}=\frac{pL}{2aZ}$  (Fig. 1). The higher the device  $V_{GS(off)}$ , for a given family, the lower the  $r_{DS}$ . The larger the inside diameter of a hose, the lower the resistance to the water flow.

9.  $\mathbf{C}_{\text{iss}}$ ,  $\mathbf{C}_{\text{rss}}$  — Input Capacitance, Reverse Transfer Capacitance

A measure of the active area of the FET. Simply a reading of  $C \doteq \epsilon \frac{A}{D}$ . Devices with higher  $I_{\text{DSS}}$ , lower  $r_{\text{DS}}$  for a  $V_{\text{GS}(\text{off})}$  generally have higher capacitance. Similarly the hose that handles more water/hr. will have a larger outside diameter.

#### 10. $I_{DSS}$ , $r_{DS}$ , $Y_{fs}$ , $V_{(BR)GSS}$ Interaction

By keeping the same size device ( $C_{iss}$ ,  $C_{rss}$  = Constant), by narrowing the drain to gate spacing, we lower the breakdown and increase the current capacity. A two inch O.D. hose may have 1/16'' thick walls or even 1/4'' thick walls, greatly varying the water flow rate.

### ${f P}_{\!\!\! m arameter}$ Tradeoffs

Just as we can design hoses in various ways; greater outside diameter, thinner walls, stronger material, oval rather than round, several circular hoses connected in parallel, less leaky connectors, FET Design is a compromise to optimize those parameters that are critical at the expense of others.

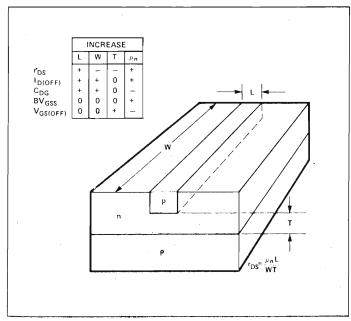

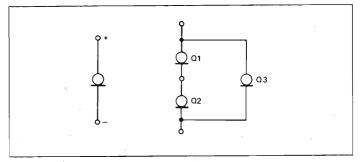

Figure I shows JFET parameter-geometry relationships.

Fig. 1. FET Parameter-Geometry Relationship

| In                   | creasing Dimension        | L | Z | 2a | The |

|----------------------|---------------------------|---|---|----|-----|

| $Y_{fs}$             | Transadmittance           | _ | + | +  | _   |

| I <sub>DSS</sub>     | Max. Drain Current        | _ | + | +  | _   |

| V <sub>GS(OFF)</sub> | Cut-Off Voltage           | 0 | 0 | +  | 0   |

| r <sub>DS</sub>      | On Resistance             | ÷ | _ | _  | +   |

| C <sub>iss</sub>     | Gate Capacitance          | + | + | 0  | +   |

| I <sub>GSS</sub>     | Gate Leakage              | ÷ | + | 0  | 0   |

| e <sub>n</sub>       | Short Circuit Input Noise | = |   | _  | +   |

| i <sub>n</sub>       | Input Current Noise       | + | + | 0  | 0   |

| Yos                  | Output Admittance         | - | + | +  | +   |

| V <sub>(BR)GSS</sub> | Breakdown Voltage         |   | 0 | 0  | +   |

#### Choices

By design, key features such as  $r_{\text{SS}} < 5$  ohms, BV<sub>DGO</sub> > 300 V,  $C_{iss} < 2$  pF can be designed individually into various FETs. Teledyne selection guides can quickly help you narrow your choice for a particular application, and eliminate problem parameters.

## Low Noise FETs - A Challenge to Low Noise Bi-Polars

#### Introduction

Field Effect Transistors were traditionally used in applications requiring high source impedances.

For low noise applications, the "rule of thumb" has been to use a FET when source impedances  $\geqslant$  100k ohms are necessary.

Times have changed and now the designer must reevaluate how FET versus bi-polar transistor amplifiers compare. A close scrutiny of bi-polar and FET specifications, along with circuit breadboarding, will startle most designers. Currently available junction N-Channel FETs, such as the 2N5391-6 and 2N4867-9, exhibit noise figures equivalent to the best bi-polar transistors with source impedances less than 10k ohms — with no compromise in other desirable FET features.

This paper reviews the important noise areas including:

- 1. Important considerations in the determination of noise figure.

- 2. Basic definitions.

- 3. Simplified test procedures.

- 4. The use of Equivalent Noise and Current Sources.

- 5. Comparative performance of the low noise FET versus bi-polar transistors.

- a. Low frequency considerations.

- b. Source impedance considerations.

- c. Other FET advantages.

#### Types of Noise

Thermal noise, excess noise, and shot noise are three of the more important types of noise phenomena inherent

in both bi-polar and FET transistors.

- 1. Thermal Noise is characterized by a condition of thermodynamic equilibrium; that is, at any specific temperature the associated noise power of a transducer with a specified noise bandwidth equals the product of 4 x Boltzmann's constant (k), absolute temperature in degrees Kelvin, and the noise bandwidth (B) in hertz. 2. Excess Noise in semiconductors results from random fluctuations in conductivity and surface effects. The spectral density of excess noise varies with the reciprocal of frequency and is usually referred to as the "I/f" noise. Negligible in low noise FETs, this "I/f" noise increases approximately 3dB per octave below a certain frequency in bi-polars, often 100 Hz.

- 3. Shot Noise is associated with the flow of do currents and is negligible above 1 kHz for most semiconductors.

#### **Accurate Noise Figure Measurements**

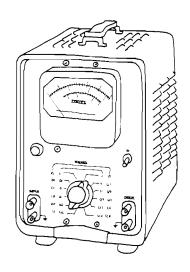

Many methods of noise figure measurements are used in the industry. The commercially available Quan Tech 2236 Control and 2237 Filter Unit is a flexible piece of equipment useful for all but a few exotic requirements. Juryrigged equipment will work equally well, although it is slower for quantity testing. Three of the common methods in use are:

1. CW-Signal Generator Method — Utilizes a calibrated signal generator and a true RMS power meter to determine the frequency dependency of transducer gain and the transducer noise bandwidth. From this informa-

tion, the output noise resulting from the input termination and the noise factor of the transducer can be determined. This is the most commonly used method.

2. Dispersed-Signal Method — Utilizes a calibrated white noise source such as a noise diode and a precision attenuator. By switching the attenuator in and out, the output noise can be separated into that generated by the transducer and that generated by the noise source.

3. Comparison Method — Compares the transducer under test and a standard transducer of the same type with a known noise factor. This method is satisfactory for go/no-go testing provided an accurate reference unit is obtained through a more precise method.

Noise figure is defined as the ratio of the signal-to-noise power ratio at the input to that at the output. It varies as a function of the input impedance, frequency, and operating current level. Measurement difficulty is encountered in determining low noise figure values accurately, particularly with source impedances greater than 100k ohm. With 100k ohm source impedance, the 2N5391-6 devices contribute little noise compared to the source impedance noise.

#### Equivalent Noise Voltages — Voltage (en), Current (in)

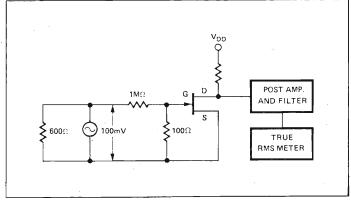

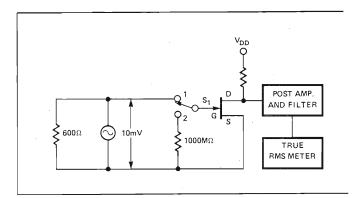

A more meaningful and useful method of Bi-Polar and Field Effect Transistor noise figure measurements is to convert "e," and "i," measurements to noise figure in dB as a function of a specified source resistance. In any active device, junction-transistor or FET, there is a certain amount of noise "ea" (referred to the input) that is independent of source impedance. There is another noise component, "i,", whose effect is directly dependent on source impedance. "e," is the equivalent noise voltage for a one hertz bandwidth. " $\sqrt{e_n^2}$ " represents the spectral density of the equivalent short-circuit noise voltage generator at the input of the FET at a specified frequency and bandwidth. The equivalent input noise voltage is determined by meas. uring the device noise output with the input ac shorted. Input referred noise is the output voltage divided by the circuit gain. For practical measurement purposes, Rg = 100 ohms is a sufficient input ac short as illustrated in Figure 1. A similar procedure is used for bi-polars except base current is supplied to obtain the desired collector

1. Set signal generator for 100mV.

2. Then

$$V_{g_3}=0.1\,\frac{(100\Omega)}{(10^6\Omega)}=10^{-5}=10\mu V$$

- 3. Set total gain to 1000.

- 4. VTVM at output now reads 10mV.

- 5. Short out  $100\Omega$  resistor.

- 6. VTVM now reads 1mV for every microvolt of noise.

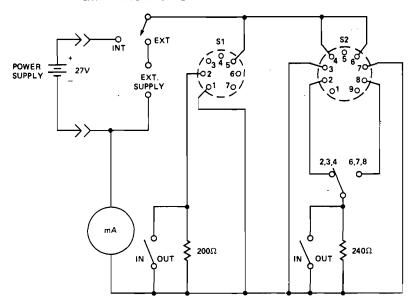

Fig. 1.

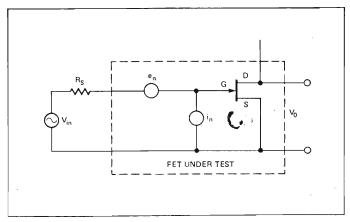

"i," is the equivalent noise current for a one hertz ba width. " $\sqrt{i_n}$ " represents the spectral density of the equ lent open-circuit noise current generator at the input of transistor at a specified frequency and bandwidth. Equalent input noise current is determined by dividing output noise (with the input ac open circuited) by the cuit gain and input ac impedance. For practical measument purposes, Rg =  $1000M\Omega$  is a sufficient input ac opas illustrated in Figure 2.

- 1. Set signal generator for 10mV with S1 in position

- 2. Set total gain to 10.

- 3. VTVM now reads 100 mV.

- 4. Switch S1 to position 2.

- 5. Meter reads one mV for each 10<sup>-13</sup> A (0.1pA) of noi:

Fig. 2.

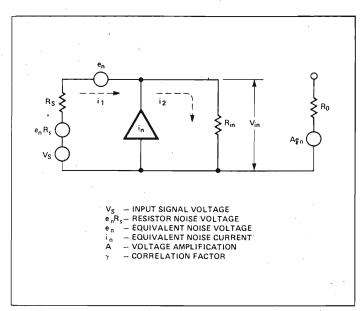

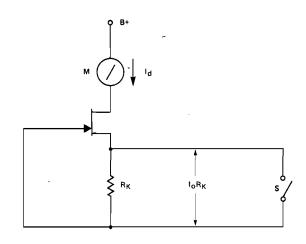

Noise voltage and current are functions of frequency. I FETs the former increases while the latter decreases wit decreasing frequency. The noise sources are relativel independent of drain current and drain-to-source voltage wich is unlike the strong dependence of the noise source on collector current in a transistor. The basic equivaler noise source circuit is shown in Figure 3.

Fig. 3. Equivalent Noise Sources

## Noise Figure Conversion From Equivalent Noise Sources

Device noise can be expressed in terms of power or voltage gains and, when expressed in dB noise figure, the two methods are the same.

In calculating noise figure from the equivalent noise sources, a correlation factor ( $\gamma$ ) exists influencing the NF as expressed in equation (8). The correlation factor is the

result of the random nature of noise, specifically the instantaneous noise voltage and noise current peaking at different intervals (random period). y may be treated like the cosine of the angle between  $e_n$  and  $i_n R_s$ . If the phase difference is zero, the cosine  $< 0^{\circ} = 1$ . This is full correlation and  $\gamma = 1$ . If zero correlation is assumed, phase angle of noise current and voltage equals 90°, and  $\gamma = 0$ .

It is widely accepted through test results that  $\gamma = 1$  is a closer approximation. The curves, nomograph, and future discussion is based on this approximation.

Noise figure may be expressed as:

Fo (dB) = 10 log

$$\frac{(V_1/N_1)^2}{(V_0/N_0)^2}$$

= 20 log  $\frac{V_1/N_1}{V_0/N_0}$

where

V<sub>1</sub> = Signal voltage into transducer.

$N_i$  = Noise voltage into transducer.

$V_0$  = Signal voltage out of transducer.

$N_0$  = Noise voltage out of transducer.

For calculating the noise figure of an amplifier, the schematic in Figure 4 is useful.

Fig. 4. Amplifier Equivalent Noise Circuit

Solving for the noise factor (multiple of noise voltage obtained, other than expected from device gain, as the source resistor noise passes through the device circuit) from the equivalent circuit.

$$F = \frac{v_{in}A}{A_{\nu}v_{nRs}} = \frac{i_2A R_{in}}{A_{\nu}v_{nRs}}$$

where  $A_{\nu} = Av_{in} = \frac{A R_{in}}{R_{in} + R_s}$  (1)

where

$$A_v = Av_{in} = \frac{A R_{in}}{R_{in} + R_s}$$

Neglecting the v, voltage source from Figure 4 which does not enter into the noise equation.

$$e_{nRs} + e_n - v_{in} = i_1 R_s \tag{2}$$

$$v_{in} = i_2 R_{in} \tag{3}$$

$$i_2 = i_1 + i_2 \text{ or } i_1 = i_2 - i_2$$

(4)

Substituting (3) & (4) into (2)

$$e_{nRs} + e_n - i_2 R_{in} = i_2 R_s - i_n R_s$$

Rearranging

$$\frac{\mathbf{e}_{.R_{s}} + \mathbf{e}_{n} + \mathbf{i}_{n} \, \mathbf{R}_{s}}{\mathbf{R}_{s} + \mathbf{R}_{in}} = \mathbf{i}_{z} \tag{5}$$

Substituting (5) into (1)

$$F = \frac{AR_{in} (e_{nRs} + e_n + i_n R_s)}{A_v e_{nRs} (R_s + R_{in})}$$

(6)

Reducing the equation, adding the noise sources as the square root of the sum of the noise voltage squared and expressing in dB results in:

NF = 20 log

$$\left[\frac{e_n^2 R_s + (e_n + \gamma i_n R_s)^2}{e_n^2 R_s}\right]^{\frac{1}{2}}$$

(7)

NF = 10 log

$$\left[1 + \frac{e_n^2 + i_n^2 R_s^2 + 2\gamma e_n i.R_s}{4KTR_s}\right]$$

(8)

Where  $e_{n}^{2}_{Rs} = 4KTR_{s}$  and

$K = 1.38 = 10^{-23}$  joules per degrees Kelvin

T = Absolute temperature in degrees Kelvin

B = Bandwidth

Now assume  $\gamma=1$  (Worst Case Noise Figure) and Bandwidth = 1 then:

NF = 10 log

$$\left[1 + \frac{(e_n + i_n R_s)^2}{4KTR_s}\right]$$

(9)

#### **Optimized Noise Figure**

In designs where optimum noise is extremely important and the source resistance flexible, R, should be chosen to give the lowest noise. Considering Equation 8 where  $e_n =$  $10^{-9}$  volts and  $i_n = 10^{-12}$  amperes, notice that at low source resistance e, will be generally the predominant term while at high source resistance in is predominant.

The optimum source resistance for minimum noise figure can easily be obtained by taking the derivative of the terms in equation (8) with respect to R<sub>s</sub> and setting it equal to

$$\begin{split} \frac{dF}{dR_s} &= 0 = \\ \frac{4KTR_s \; (2i_n^2R_s + 2\gamma e_n i_n) - (e_n^2 + i_n^2 \; R_s^2 + 2\gamma e_n i_n \; R_s) \; 4KT}{(4KTR_s)^2} &= 0 \end{split}$$

Reducing and subtracting terms

$$i_0^2 R_1^2 = e_0^2$$

$$R_s = \frac{e_n}{i_n} \qquad \text{For NF}_{r,n} \tag{10}$$

Notice for the bi-polar transistor "i." (from Figure 6 & 7) that a typical optimum source resistance is 10k @  $10\mu$ A.

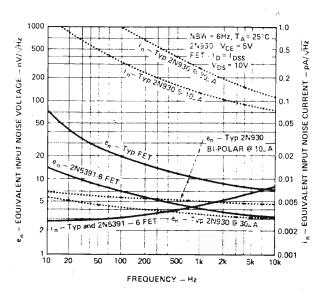

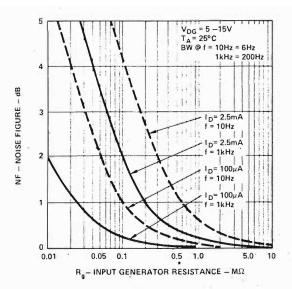

Fig. 5. Equivalent Input Noise Voltage and Current vs. Frequency

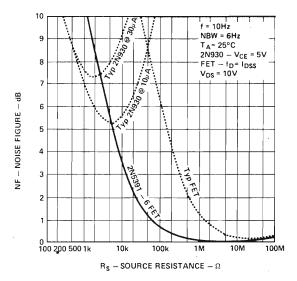

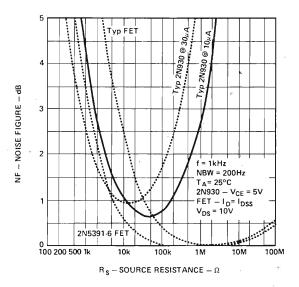

Fig. 6. Noise Figure vs. Source Resistance

Fig. 7. Noise Figure vs. Source Resistance

The 2N5391-6 field effect transistor optimum source resistance is 1 to 10M. However, even at the optimum source resistance for a typical 2N930 type bi-polar transistor, the noise figure is higher than the 2N5391-6 series FET's.

Substituting equation (10) into (8) gives

$$NF_{min} = 10 \log \left[ 1 + \frac{(e_n + \gamma e_n) 2 i_n}{4KT} \right]$$

(11)

Assuming worst case  $\tau = 1$ ,

$$NF_{min} = 10 \log \left[ 1 + \frac{e_n i_n}{KT} \right]$$

#### Bi-Polar Versus FET Noise Comparison

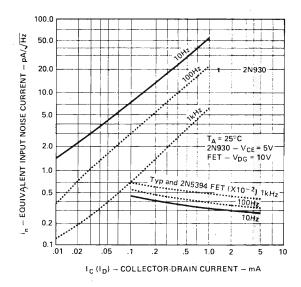

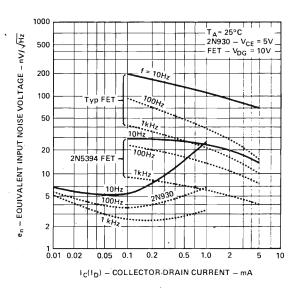

The significant difference between the bi-polar and FET is in the "e<sub>n</sub>" and "i<sub>n</sub>" values as plotted in Figure 5, 8, and 9. Bi-polars are extremely sensitive to collector current variations and the circuit designer must beware. FET's are relatively insensitive to drain current variations, particularly "i<sub>n</sub>". Notice that the FET "i<sub>n</sub>" is 2-3 orders of magnitude lower than the bi-polar.

FET devices perform particularly well at low frequencies (<100Hz) i.e., they do not show a significant I/f noise slope. Naturally at low frequencies, the noise figure drops rapidly as source resistance increases.

Fig. 8. Equivalent Input Noise Current vs. Current

Fig. 9. Equivalent Input Noise Voltage vs. Current

Most impressive about the FET, particularly the 2N5391-6 series, is its low noise over many decades of source resistance value. This flexibility is advantageous in straingauges, light sensors, thermistors, and other transducers. Designers of standard amplifier circuits who will be using varying source resistance might well use the 2N5391-6 or 2N4867-9 series FET's to provide the low noise flexibility.

If low noise applications restrict source resistances to less than 500 ohms, the bi-polar will probably continue to be the best.

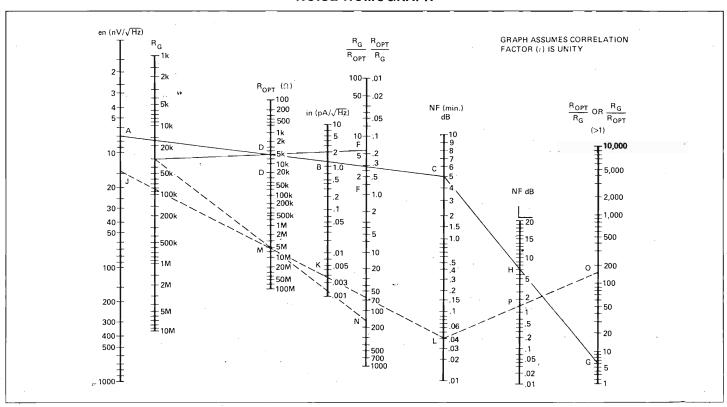

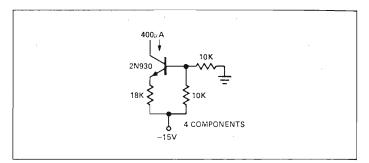

#### Noise Figure Nomograph

The Noise Nomograph is a useful method of solving the various noise equations when it is assumed that the correlation factor  $(\gamma)$  is unity, a close approximation for most devices.

The more important noise equations are:

NF = 10 log

$$\left[1 + \frac{(e_n + i_n R_s)^2}{4KTRg}\right]$$

(1)

$$NF_{min} = 10 \log \left[ 1 + \frac{e_n i_n}{KT} \right]$$

(2)

$$\mathsf{R}_{\mathsf{opt}} = \frac{\mathsf{e}_{\mathsf{n}}}{\mathsf{i}_{\mathsf{n}}} \tag{3}$$

Example using the nomograph:

Choose between using a 2N5391-6 series FET and a 2N930 bi-polar transistor in a low noise amplifier with 30k ohm input impedance where 10Hz noise is critical.

2N930 (

$$I_C = 10\mu A$$

)  $e_n = 7nV/\sqrt{Hz}$

$I_n = 1.5pA/\sqrt{Hz}$

2N5391-6 Series FET  $e_n = 14nV/\sqrt{Hz} i_n$

$= .0028pA/\sqrt{Hz}$

#### Solution

- A. Determine 2N930 Noise Figure

- 1. Connect "A"  $e_n$  (7nV/ $\sqrt{Hz}$ ) and "B"  $i_n$  (1.5pA/ $\sqrt{Hz}$ ) points with a straight line to "C", NF<sub>min</sub> = 5.1 dB.

- 2. Connect "E"  $(R_g = 30k\Omega)$  and "D"  $(R_{opt} = 5k\Omega)$  points with a straight line to "F"  $(R_g/R_{opt} = 6)$ .

- 3. Transfer "F" to "G" on  $\frac{R_{opt}}{R_g}$ ,  $\frac{R_a}{R_{opt}}$  scale and connect

- points "C" & "G" with a straight line.

- 4. Determine the intersection of this line and the NF scale "H" read 7.5 dB noise Figure.

- B. Determine 2N5391-6 Series Noise Figure

- 1. Connect 'J''  $e_n$  (14nV/ $\sqrt{Hz}$ ) and "K"  $i_n$  (.0028pA/ $\sqrt{Hz}$ ) points with a straight line to "L", NF<sub>min</sub> = 0.04 dB.

- 2. Connect "E" ( $R_g=30k\Omega$ ) and "M" ( $R_{opt}=5M\Omega$ ) points with a straight line to "N" ( $R_{opt}/R_g=160$ ).

- 3. Transfer "N" to "O" on  $R_{\text{sp}}$ ,  $/R_{\text{g}}$ ,  $R_{\text{g}}/R_{\text{opt}}$  scale and connect points "L" and "O" with a straight line.

- 4. Determine the intersection of this line and the NF scale "P" read 1.6 dB noise figure.

- C. From the above solutions using the Noise Nomograph the 2N5391-6 series FET's would have the lower noise by 5.9 dB and be the much better choice.

#### **NOISE NOMOGRAPH**

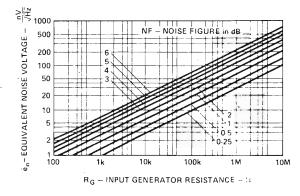

Fig. 10. Noise Figure—Noise Voltage Conversion Chart

#### **Noise Voltage Conversion Chart**

Practically all junction FETs being manufactured today

have  $e_n$  sufficiently low that it can be neglected for Gen erator Resistance values up to 10 Megohms. On this basis the simplified approximate chart can be used as given in Figure 10.

#### **Bibliography**

- 1. Joel M. Cohen, "How to Measure FET Noise," Electron ics (Nov. 30, 1964).

- 2. John D. Skipper, "Cut Operational-Amplifier Noise, Electronic Design (Sept. 13. 1967).

- EIA Standard RS-354, "The Measurement of Transistor Equivalent Noise Voltage and Equivalent Noise Current at Frequencies up to 20kHz," April, 1968.

- EIA Standard RS-353, "The Measurement of Transistor Noise Figure at Frequencies up to 20kHz by Sinusoidal Signal-Generator Method," April 1968.

- 5. Teledyne Semiconductor, "Field Effect Transistors Theory and Application," Technical Bulletin No. 1, May 1971.

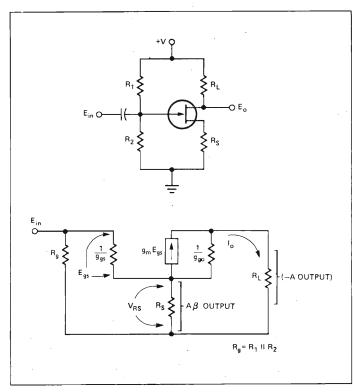

## FET Small-Signal Analysis

Analysis of low-frequency, small-signal field-effect transistor amplifier stages can be accomplished with practical accuracy by using simple equations. The techniques described here provide general coverage of operation slightly over 100 kHz. If capacitance effects are included, the equations will be useful into the megahertz region.

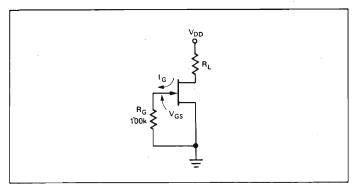

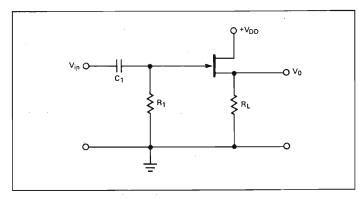

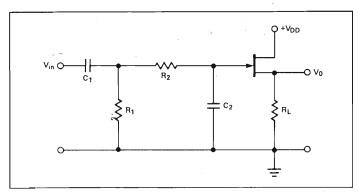

#### **Common-Source Amplifier**

The schematic for a common-source amplifier and its equivalent circuit is shown in Fig. 1. Capacitance has been omitted and is neglected in the derivation that follows. Also, if it is assumed that negligible current flows into  $R_{\rm g}$ , then

$$\frac{1}{g_{as}} + R_g >> R_L \text{ or } R_S$$

#### Voltage Gain

Referring to the equivalent circuit (Fig. 1),

$$A_{v} = -\frac{A}{1 + A\beta}$$

where

and

$$-A = \frac{e_o}{E_{gs}}$$

$$A\beta = \frac{V_{RS}}{E_{GS}}$$

Solving for the output current

$$I_{o} = g_{m} E_{gs} \left( \frac{\frac{1}{g_{o}}}{\frac{1}{g_{o}} + R_{L} + R_{S}} \right) =$$

$$g_{m} E_{gs} \left[ \frac{1}{1 + g_{o} (R_{L} + R_{S})} \right]$$

Since

$$-A = -\frac{I_o R_L}{E_{as}}$$

Fig.1. FET common-source amplifier schematic and equivalent circuit.

then

$$-A = \frac{-g_m R_L}{1 + g_o (R_L + R_S)}$$

Also

$$A\beta = \frac{I_o R_S}{E_{gs}} = \frac{g_m R_S}{1 + g_o (R_L + R_S)}$$

and

$$A_{v} = \frac{\frac{-g_{m} R_{L}}{1 + g_{o} (R_{L} + R_{S})}}{1 + \frac{g_{m} R_{S}}{1 + g_{o} (R_{L} + R_{S})}}$$

$$A_{v} = \frac{-g_{m} R_{L}}{1 + g_{o} (R_{L} + R_{S})}$$

However, if  $g_o(R_L + R_S) << 1$ , then

$$A_V \approx \frac{-R_L}{\frac{1}{q_m} + R_S}$$

#### Input Impedance

The total input impedance  $(Z_{int})$  is equal to  $R_g$  in parallel with the impedance  $(Z_{in})$  seen at the gate terminal.

Solving for the gate terminal impedance,

$$Z_{in} = \frac{\frac{1}{g_{gs}}}{1 - A_{vs}}$$

where  $A_{vS}$  (gate to source voltage gain) =  $V_{RS}/E_{in}.$  However, since  $V_{RS}=E_{in}-E_{gs}$  and

$$E_{gs} = \frac{V_{RS}}{A\beta} = \frac{\frac{V_{RS}}{g_{m} R_{S}}}{1 + g_{o} R_{L} + g_{o} R_{S}}$$

then

$$\begin{split} V_{RS} &= E_{in} - \frac{\frac{V_{RS}}{g_m \, R_S}}{1 + g_o \, R_L + g_o \, R_S} \\ V_{RS} &= \frac{E_{in} \, g_m \, R_S}{1 + g_o \, (R_L + R_S) + g_m \, R_S} \end{split}$$

and

$$A_{VS} = \frac{V_{RS}}{E_{In}} = \frac{g_{m} R_{S}}{1 + g_{o} (R_{L} + R_{S}) + g_{m} R_{S}}$$

Therefore.

$$Z_{in} = \frac{\frac{1}{g_{gs}}}{1 - \frac{g_{m} R_{s}}{1 + g_{s} (R_{L} + R_{s}) + g_{m} R_{s}}}$$

and

$$Z_{i-1} = R_g \frac{\frac{1}{g_{gs}}}{1 - \frac{g_m R_s}{1 + q_o (R_1 + R_s) + g_m R_s}}$$

#### **Bootstrapping**

The impedance  $R_{\rm g}$  is often the limiting factor when trying to obtain the highest possible input impedance. To increase the effective impedance of  $R_{\rm g}$ , a bootstrapping technique can be employed as shown in Fig. 2.

For this circuit,

$$Z_{st} = \frac{R'_g}{1 - A_{VS}} \left\| \frac{1}{g_{gs}} \right\|$$

Fig. 2. Schematic and equivalent circuits of FET bootstrapping technique.

and with  $R_{\text{b}}$  in parallel with  $R_{\text{s}},$  the  $A_{\text{vs}}$  equation derived previously is modified to

$$A_{VS} = \frac{g_{m} \left( \frac{R_{S} \, R_{b}}{R_{S} + R_{b}} \right)}{1 + (g_{m} + g_{o}) \frac{R_{S} \, R_{b}}{R_{S} + R_{b}} + g_{o} \, R_{L}}$$

Note that for the  $Z_{\rm int}$  equation  $A_{\rm VS}$  being less than unity raises both impedance factors to be paralleled.

The effect of  $A_{VS}$  on  $g_{gs}$  also applies to the gate-to-source capacitance.

$$C_{gs}$$

equivalent =  $C_{gs}$  (1 -  $A_{vs}$ )

The gate-to-drain capacitance  $C_{\rm gd}$  must be considered with due appreciation for the Miller effect. The Miller effect is simply an apparent multiplication of the capacitance.

$$C_{gd}$$

equivalent =  $C_{gd}$  (1 +  $|A_v|$ )

where  $\left|A_{\nu}\right|$  is the absolute value of the gate-to-drain voltage gain.

The most significant effect on circuit performance is caused by  $C_{\rm gd}$  and by comparison,  $C_{\rm gs}$  generally can be neglected. For this reason many specification sheets do not list the value of  $C_{\rm gs}$ .

#### **Output Impedance**

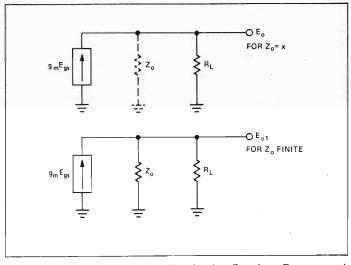

The total output impedance  $(Z_{OT})$  is equal to  $R_c | Z_o$  where  $Z_o$  is the impedance looking into the drain terminal. To determine the values of  $Z_o$ , first find the change in output voltage resulting from a  $\Delta$  shift in  $R_1$ . Two equations evolve

depending on whether  $1/g_o$  is finite ( $\Delta E_o$ ) or  $1/g_o$  is infinite ( $\Delta E_o$ ).

$$\Delta \; E_{\text{OI}} \approx \frac{-\; E_{\text{in}} \; g_{\text{m}} \; \cdot}{1 + g_{\text{o}} \; (R_{\text{L}} + R_{\text{S}}) + g_{\text{m}} \; R_{\text{S}}} \; \Delta \; R_{\text{L}} \label{eq:delta_energy}$$

when 1/go is finite, and

$$^{1}\Delta$$

$E_{o} \approx \frac{-E_{in} g_{m}}{1 + g_{m} R_{S}} \Delta R_{L}$

when 1/go is infinite.

The per unit difference in these equations is a measure of the output impedance relative to  $R_{\rm t}$ .

$$\begin{split} \frac{\Delta \, E_o \, - \Delta \, E_{01}}{\Delta \, E_{01}} \\ &= \frac{-E_{in} \, g_m \, \Delta \, R_L}{1 + g_m \, R_S} + \frac{E_{in} \, g_m \, \Delta \, R_L}{1 + g_o \, (R_L + R_S) + g_m \, R_S} \\ &\qquad \qquad \frac{E_{in} \, g_m \, \Delta \, R_L}{1 + g_o \, (R_L + R_S) + g_m \, R_S} \\ &\qquad \qquad \Delta \, E_o - \Delta \, E_{01} \\ &\qquad \qquad \Delta \, E_{01} = \frac{g_o \, (R_L + R_S)}{1 + g_m \, R_S} \end{split}$$

From the equivalent circuits of Fig. 3 calculate

$$Z_{o}$$

from  $\frac{\Delta \; E_{o} - \Delta \; E_{01}}{\Delta \; E_{01}}$  as follows:

$$\frac{\frac{\Delta \, E_o - \Delta \, E_{01}}{\Delta \, E_{01}}}{\frac{B_{gs} \, R_L - g_m \, E_{gs} \left(\frac{Z_o \, R_L}{Z_o + R_L}\right)}{g_m \, E_{gs} \left(\frac{Z_o \, R_L}{Z_o + R_L}\right)} \approx \frac{R_L}{Z_o}$$

and

$$Z_{o} = \frac{R_{L}}{\frac{\Delta E_{o} - \Delta E_{01}}{\Delta E_{01}}} = \frac{1 + g_{m} R_{S}}{g_{o} (R_{L} + R_{S})} (R_{L})$$

If there had been no source resistance  $R_s$ , the device output impedance would have been  $1/g_\circ$  as indicated by the equivalent circuit (Fig. 1). The effect of the local degeneration resistor  $R_s$  has reduced the output admittance to

$$\left[\frac{g_o}{1+g_mR_c}\right]\left[\frac{R_L+R_s}{R_L}\right]$$

Fig. 3. Common-source output circuits for E  $_{\!o}$  when  $Z_{\!o}=\infty$  and E  $_{\!o}$  , when Z  $_{\!o}$  is finite.

The total output impedance now becomes

$$Z_{\text{OT}} = \frac{R_{\text{L}} \left( \frac{1 + g_{\text{L}} R_{\text{S}}}{g_{\text{D}}} \right) \left( \frac{R_{\text{L}}}{R_{\text{L}} + R_{\text{S}}} \right)}{R_{\text{L}} + \left( \frac{1 + g_{\text{L}} R_{\text{S}}}{g_{\text{O}}} \right) \left( \frac{R_{\text{L}}}{R_{\text{L}} + R_{\text{S}}} \right)}$$

$$Z_{OT} = \frac{R_{L} \frac{1 + g_{m} R_{s}}{g_{o}}}{R_{L} + R_{s} + \frac{1 + g_{m} R_{s}}{g_{o}}}$$

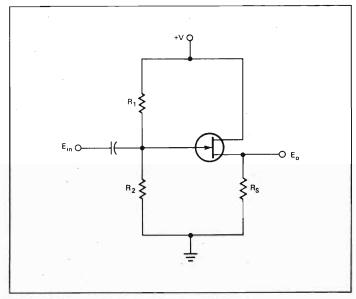

#### SOURCE FOLLOWER CIRCUIT

The schematic for a source follower circuit is shown in Fig. 4.

Fig. 4. Schematic of FET source follower circuit.

#### Voltage Gain

The same argument that was used to calculate  $A_{VS}$  for the common-source amplifier can be used to calculate the voltage gain for the source follower but with  $R_L$  equal to zero. Thus,

$$A_{VS} = \frac{g_m R_S}{1 + R_S (g_m + g_o)}$$

#### Input Impedance

$$Z_{int} = R_g || Z_{in} \text{ where } R_g = R_1 || R_1 || R_2 ||$$

$$Z_{in} = \frac{\frac{1}{g_{gs}}}{1 - \frac{g_m R_s}{1 + R_s (g_m + g_o)}}$$

and

$$Z_{int} = R_g \left\| \frac{\frac{1}{g_{gs}}}{1 - A_{vs}} \right\|$$

#### **Output Impedance**

The total output impedance  $Z_{\text{OT}}=R_{\text{S}}\parallel Z_{\text{o}}.$   $Z_{\text{o}}$  can be derived from the basic gain equation as follows:

$$A_{v} = \frac{g_{_{m}} \, R_{_{S}}}{1 + R_{_{S}} \, (g_{_{m}} + g_{_{o}})} = \frac{R_{_{S}}}{\frac{1}{g_{_{m}}} + R_{_{S}} \, \frac{g_{_{o}}}{g_{_{m}}} + R_{_{S}}} = \frac{E_{_{out}}}{E_{_{in}}}$$

The above equation is in the form of a voltage divider as shown in Fig. 5. Thus it can be seen that the FET output impedance  $(Z_{\circ})$  is

$$Z_{\circ} = \frac{1}{g_{m}} + R_{S} \frac{g_{\circ}}{g_{m}}$$

The total output impedance Zot is

$$Z_{OT} = \frac{\frac{R_s}{g_m} + \frac{g_o}{g_m} R_s^2}{\frac{1}{g_o} + R_s \frac{g_o}{g_o} + R_s} = \frac{R_s + g_o R_s^2}{1 + R_s (g_o + g_m)}$$

$$\mbox{As } g_o \rightarrow 0, \ \ Z_{\mbox{\scriptsize OT}} \rightarrow \frac{R_{\mbox{\scriptsize S}}}{1 + R_{\mbox{\scriptsize S}} \, g_{\mbox{\tiny m}}} = R_{\mbox{\scriptsize S}} \mid \mid \frac{1}{g_{\mbox{\tiny m}}}$$

Fig. 5. Voltage divider equivalent of source follower output circuit.

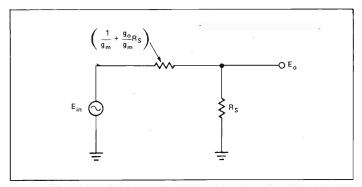

#### **COMMON-GATE AMPLIFIER**

The common-gate amplifier and its equivalent circuit are shown in Fig. 6. This circuit is not mentioned in most literature but is important primarily in the analysis of feedback amplifiers.

Fig. 6. Schematic and equivalent circuit of FET common-gate

#### **Voltage Gain**

The gain equation is identical to that for the commonsource amplifier except that no phase inversion occurs.

$$A_{v} = \frac{g_{m} R_{L}}{1 + g_{o} (R_{L} + R_{S}) + g_{m} R_{S}}$$

#### Input Impedance

Referring to the equivalent circuit Fig. 6, the current flow in the  $1/g_{\rm gs}$  branch is neglected (i.e.,

$$1/g_{gs} + R_g >> R_L + 1/g_o + R_S$$

).

$$E_{in} = i_1 \left( R_S + \frac{1}{q_0} + R_L \right) - g_m E_g \frac{1}{q_0}$$

and

$$\mathbf{E}_{q} = \mathbf{E}_{in} - \mathbf{i}_{1} \, \mathbf{R}_{S}$$

Substituting

$$\begin{split} E_{in} &= i_{1} \left( R_{S} + \frac{1}{g_{o}} + R_{L} \right) - E_{in} \frac{g_{m}}{g_{o}} + i_{1} R_{S} \frac{g_{m}}{g_{o}} \\ E_{in} \left( 1 + \frac{g_{m}}{g_{c}} \right) &= i_{1} \left( R_{S} + \frac{1}{g_{c}} + R_{L} + R_{S} \frac{g_{m}}{g_{c}} \right) \end{split}$$

$$\begin{split} \frac{E_{in}}{i_1} &= Z_{in} = \frac{R_S + \frac{1}{g_o} + R_L + R_S \frac{g_m}{g_o}}{1 + \frac{g_m}{g_o}} \\ Z_{in} &= \frac{1}{g_o + g_m} + (R_S + R_L) \frac{g_o}{g_o + g_m} + \frac{R_S g_m}{g_o + g_m} \end{split}$$

$$f g_o \ll g_n$$

then

$$Z_{\text{in}} \approx \frac{1}{g_{\text{m}}} + (R_{\text{S}} + R_{\text{L}}) \, \frac{g_{\text{o}}}{g_{\text{m}}} + R_{\text{S}}$$

And if  $(R_S + R_L) g_o << 1/g_m$ , then  $Z_{in} = 1/g_m + R_S$  where  $1/g_m$  is a dynamic impedance seen looking into the source terminal of the FET.

#### **Output Impedance**

The output impedance is identical to that of the commonsource stage.

#### SUMMARY

If the assumptions listed below are valid for the circuit in question, then the simplified equations in the chart may be used.

- (a)  $g_o(R_L + R_S) << 1$

- (b)  $g_o (R_L + R_S) << 1/g_m$

- (c)  $1/g_{\circ} >> R_L$

- (d)  $R_1 || R_2 >> g_{gs}$

- (e) Low-frequency capacitive reactances are negligible.

| PARAMETER           | COMMON SOURCE                                               | SOURCE FOLLOWER                                                       | COMMON GATE                                                                 |

|---------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 20                  | +٧ 0                                                        | +٧0                                                                   |                                                                             |

|                     | R <sub>1</sub> R <sub>2</sub> R <sub>3</sub> R <sub>8</sub> | R <sub>1</sub><br>E <sub>in</sub><br>R <sub>2</sub><br>R <sub>S</sub> | R <sub>1</sub> R <sub>2</sub> R <sub>5</sub> R <sub>5</sub> E <sub>in</sub> |

| VOLTAGE GAIN        | $A_{v} \approx \frac{-R_{L}}{\frac{1}{g_{m}} + R_{S}}$      | $A_{VS} \approx \frac{R_S}{\frac{1}{g_m} + R_S}$                      | $A_{v} \approx \frac{R_{L}}{\frac{1}{g_{m}} + R_{s}}$                       |

| INPUT<br>IMPEDANCE  | $Z_{in} \approx  R_1  R_2$                                  | $Z_{in} \approx R_i   R_2  $                                          | $Z_{in} \approx R_S + \frac{1}{g_m}$                                        |

| OUTPUT<br>IMPEDANCE | $Z_{o} \approx R_{L}$                                       | $Z_{oT} \approx R_s \left\  \frac{1}{g_m} \right\ $                   | $Z_{\circ} \approx R_{L}$                                                   |

This note was written by R. L. Greunke of Martin-Denver and originally published in the October, 1966 issue of **EDN Magazine**. Reprinted here by permission.

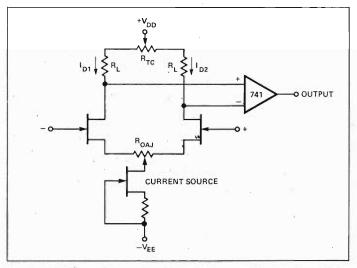

## Transadmittance Analysis

When trying to maximize voltage gain in FET amplifier circuits, the type with highest minimum guaranteed transadmittance,  $Y_{fs}$ , may seem desirable. It is not obvious that a  $Y_{fs}$  of 1000  $\mu$ mhos may out-perform a device with a  $Y_{fs}$  of 5000  $\mu$ mhos, but it is possible.

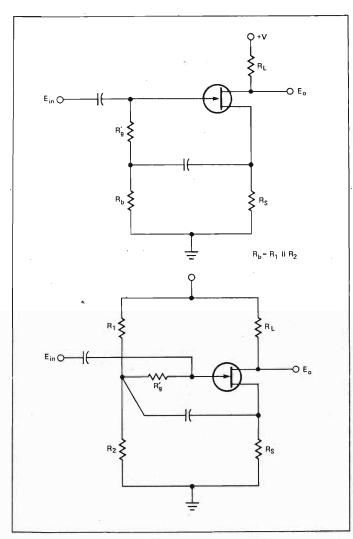

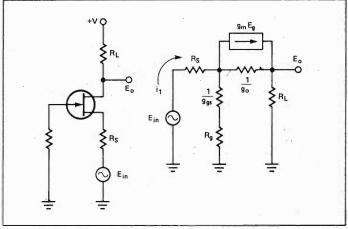

#### **CONSIDERATIONS**

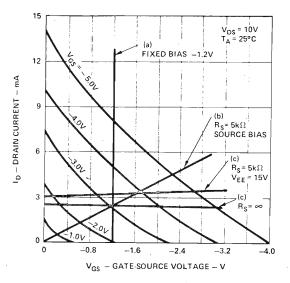

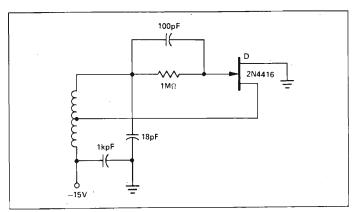

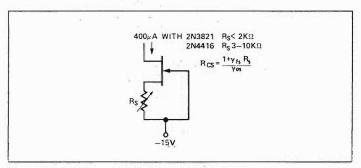

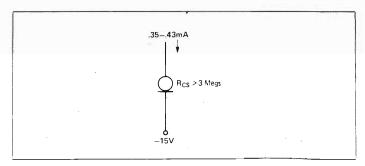

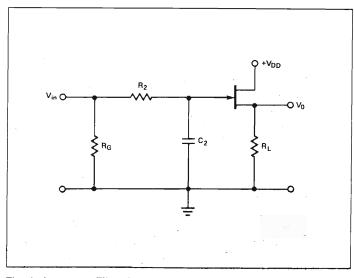

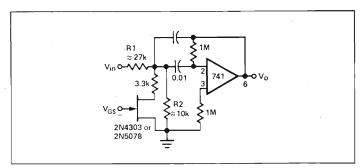

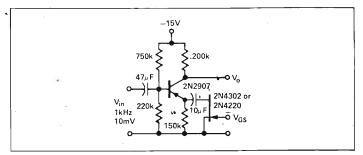

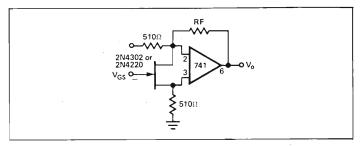

There are three major considerations in designing even a simple audio amplifier — voltage gain, distortion, and noise figure. In various applications, each takes on varying importance and the normal compromises are made. Tradeoffs are illustrated in the simple grounded source amplifier as shown in Fig. 1.

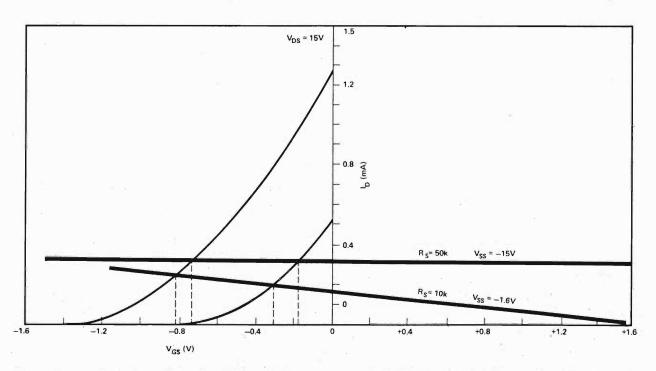

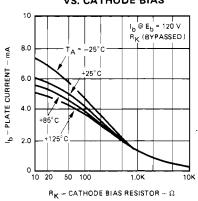

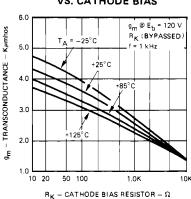

The best fixed operation would come from Fig. 1c where the current source is another FET or bi-polar current source arrangement. (See Fig. 2,  $R_5 = line$ .) Each of the different arrangements is shown using the 2N4416 (U1994E)

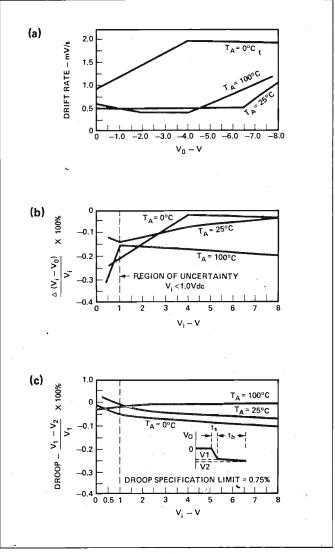

family curve as a vehicle. For example, using the extremes of the 2N4416  $I_{DSS}=5$ -15 mA with Fig. 1b  $R_S=5$ K, then  $I_D$ 0 operating current would vary from approximately 2 mA-5 mA. Each of the different modes is represented in Fig. 2.

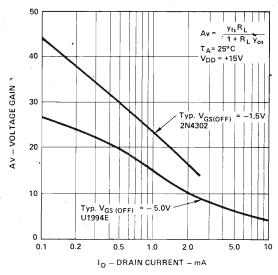

#### **VOLTAGE GAIN CONSIDERATION**

Using any one of the arrangements in Fig. 1, the familiar voltage gain expression for low frequencies ( $C_{\rm iso}$ ,  $C_{\rm res}$  negligible) is:

(Eq. 1)

$$A_V = \frac{-Y_{is}R_L}{1 + R_LY_{os}}$$

Now the question arises, how does the change in  $Y_{cs}$  with voltage,  $Y_{fs}$  with current, the magnitude of  $R_L$ , and the interaction of  $R_L$  and  $Y_{cs}$  all fit together to maximize voltage gain?

Using the basic drain current and transadmittance equations

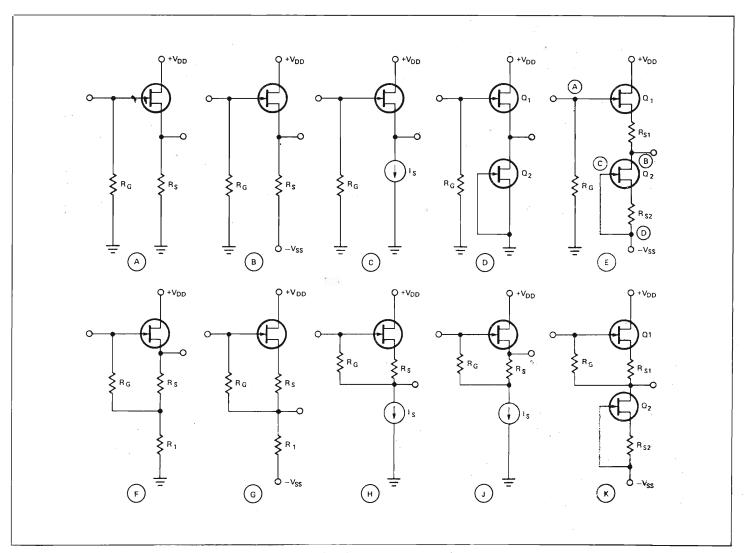

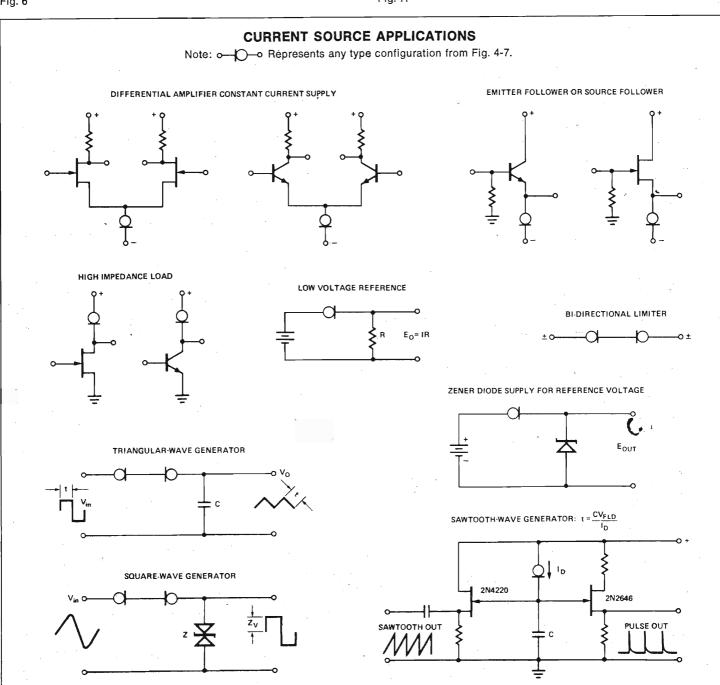

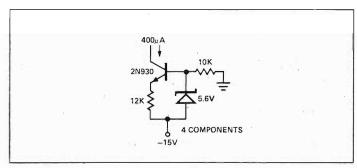

Fig. 1. N-Channel FET Bias Configurations

$$(\text{Eq. 2}) \quad I_{\text{D}} = I_{\text{DSS}} \left(1 - \frac{V_{\text{GS}}}{V_{\text{GS}(\text{OFF})}}\right)^2 \text{ & } Y_{\text{fs}} = Y_{\text{fso}} \left(1 - \frac{V_{\text{GS}}}{V_{\text{GS}(\text{OFF})}}\right)$$

where

$$Y_{\text{fso}} \stackrel{\bullet}{=} \frac{2 I_{\text{DSS}}}{V_{\text{GS}(\text{OFF})}}$$

Substituting these equations into the general voltage gain expression, we obtain

$$(\text{Eq. 3}) \quad A_{\text{V}} = \frac{-2(V_{\text{DD}} - V_{\text{DGnd}})}{V_{\text{GS(OFF)}} - V_{\text{GS}}} \ \ \text{and} \quad A_{\text{V(min)}} = -\frac{2 \, (V_{\text{DD}} - V_{\text{DGnd}})}{V_{\text{GS(OFF)}}}$$

The  $A_{V_{(min)}}$  equation really becomes a device figure of merit when unlimited supply voltage is available by substituting  $V_{(BR)GSS}$  for  $V_{DD}$  -  $V_{DGnd}$ . This is fine but in most cases, a finite  $V_{DD}$  supply is available. Practically speaking the minimum voltage that can operate  $V_{DG}$  (not  $V_{DS}$ ) in a device is the device  $V_{GS(OFF)}$ , but preferably  $V_{GS(OFF)}$  + 2 V. If we use the preferable voltage minimum, then:

Fig. 2. FET Bias Operating Conditions

(Eq. 4)

$$R_L = \frac{V_{DD} - V_{GS(OFF)} - 2}{I_D}$$

#### **VOLTAGE GAIN EXAMPLE**

Again using the curves applicable to the 2N4416 (U1994E) and its derivatives such as the 2N4302, a table and graph can be constructed to analyze Fig. 1c in conjunction with Equation 1 and 4. Assume  $V_{\text{DD}}=+15\,\text{V},\ V_{\text{EE}}=-15\,\text{V},$  and  $R_s=\infty$  bypassed current source. Ambient temperature  $25^{\circ}\text{C}$

Fig. 3. Comparative Voltage Gains

| ·                                            |                |                                   | I <sub>D</sub> Value |              |              |                              |              |               |  |

|----------------------------------------------|----------------|-----------------------------------|----------------------|--------------|--------------|------------------------------|--------------|---------------|--|

| Test                                         | Units          | <b>V</b> <sub>es</sub> = <b>0</b> | 2.5 mA               | 1 mA         | 0.5 mA       | 0.2 mA                       | 0.1 mA       | _ Device* No. |  |

| Y <sub>fs</sub>                              | μ <b>mh</b> os | 3500<br>5500                      | 3500<br>3350         | 2800<br>2500 | 2050<br>1800 | 1200<br>1100                 | 675<br>575   | A<br>B        |  |

| Y <sub>os</sub>                              | μ <b>mh</b> os | 35<br>90                          | 35<br>50             | 27<br>40     | 20<br>30     | 13<br>20                     | 7<br>10      | A<br>B        |  |

| R <sub>L</sub>                               | Kohms          | 4.6K<br>0.57K                     | 4.6K<br>3.2K         | 11.5K<br>8K  | 23K<br>16K   | 57.5 <b>K</b><br>40 <b>K</b> | 115K<br>80K  | A<br>B        |  |

| Calculated<br>Voltage Gain<br>A <sub>V</sub> |                | 13.8<br>3.0                       | 13.8<br>9.2          | 24.0<br>15.2 | 28.5<br>19.5 | 39.0<br>24.4                 | 43.0<br>25.5 | A<br>B        |  |

$$^*A - V_{GS(OFF)} = -1.5 V$$

$I_{DSS} = 2.5 \text{ mA}$

$$B - V_{GS(OFF)} = -5.0 \text{ V}$$

$I_{DSS} = 14 \text{ mA}$

From Fig. 3 one can conclude that strictly on a voltage gain basis, it is better to select a lower  $I_{DSS}$ ,  $V_{GS(OFF)}$  unit such as the 2N4302, 2N4220 instead of units featuring higher  $Y_{r_S}$  minimum such as the 2N4416, U1994E combination. As will be discussed, this is completely valid when input signal swings are only a few millivolts.

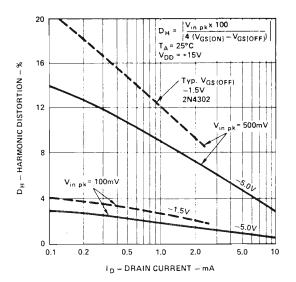

#### **DISTORTION CONSIDERATIONS**

The FET, unlike other semiconductor devices and vacuum tubes, follows the square law curve closely. Thus, li e beyond the second harmonic is present with any incoming sine wave. By combining the DC and AC components of gate-source voltage in Equation 2, harmonic distortion can be determined.

By definition:

(Eq. 5)

$$D_H$$

(%) =  $\frac{V_{rms} \text{ of 2nd harmonic}}{V_{rms} \text{ of fundamental}} \times 100 = \frac{V_{in[peak]} (100)}{V_{GS op} - V_{GS(OFF)}}$

In this case, the higher  $V_{\text{GS}(\text{OFF})}$  device operated further away from cutoff (near  $V_{\text{GS}}=0$  — more linear portion of the transfer curve — Fig. 2), will reduce distortion. Likewise tne harmonic distortion is directly proportional to the peak input signal. If only a few millivolts, the device  $V_{\text{GS}(\text{OFF})}$  has a negligible effect on distortion.

Typical input signals usually consist of complex waveforms of several frequencies, resulting in intermodulation distortion from the harmonics present. By combining the DC and AC components of gate-source voltage, by definition:

$$\begin{split} D_{\text{iM}} &= \frac{V_{\text{rms}} \text{ of intermodulation components}}{V_{\text{rms}} \text{ of fundamental}} \times 100 = \\ &\frac{V_{\text{in1}} \cdot V_{\text{in2}} (100)}{1.4 (V_{\text{GS op}} - V_{\text{GS(OFF)}} V_{\text{in1}}^2 + V_{\text{in2}}^2} \end{split}$$

Just as for D<sub>H</sub>, Equation 5, intermodulation distortion is minimal for operation near  $V_{\text{GS op}}=0$  and for higher  $V_{\text{GS(OFF)}}$  devices, although slight. The amplitude of the input signals is most significant.

#### HARMONIC DISTORTION EXAMPLE

A similar table and graph using Eq. 5 can be constructed for the same type of devices as for voltage gain.

From Fig. 4 one can conclude that for 100 mVpk, there is a negligible difference in harmonic distortion over a wide range of device  $V_{\text{GS(OFF)}}$  and operating current. At higher levels, the difference becomes significant. The same type of curves would be generated for intermodulation distortion.

To reduce distortion, at the expense of voltage gain, feedback such as an unbypassed source resistor,  $R_{\text{5}}$ , can be used. In this case, distortion is reduced by the product

Fig. 4. Comparative Harmonic Distortion

Fig. 5. Comparative Noise Figure

of  $(1+Y_{fs}R_s)$ . For calculations, this term is added to the denominator of both Eq. 5 and 6.

#### NOISE FIGURE CONSIDERATIONS

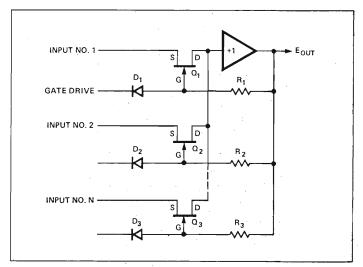

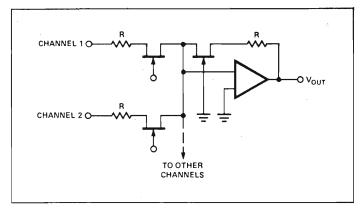

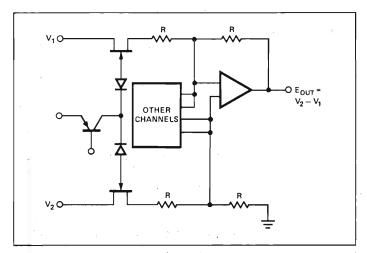

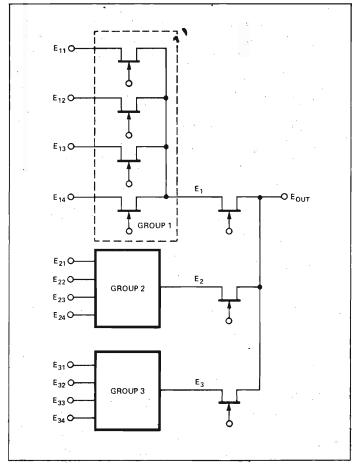

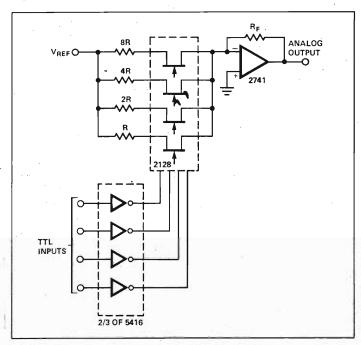

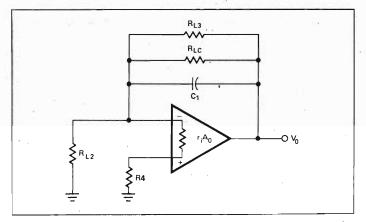

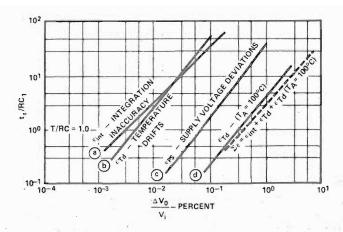

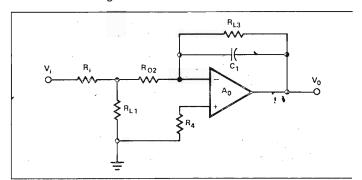

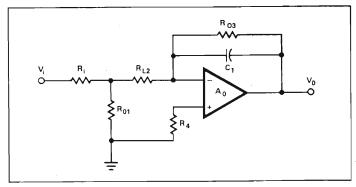

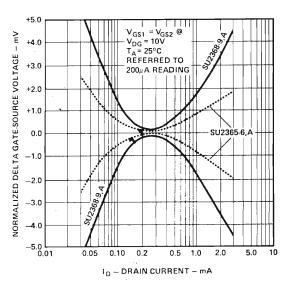

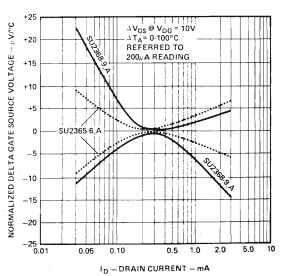

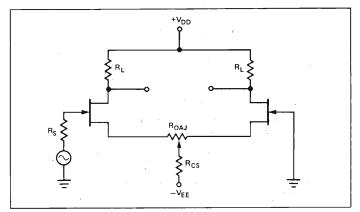

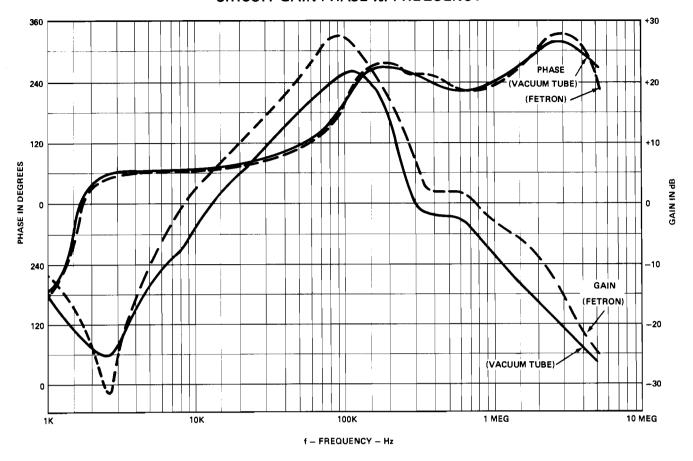

For thorough discussion, consult the Teledyne application note "Low Noise FETs — A Challenger to Low Noise Bi-Polars." Since total noise is a function of so many different variables, no direct correlation can be established other than the affect of  $R_{\rm g}$  and f on noise. The main point is that above 500K  $R_{\rm g}$ , the Noise Figure variation is negli-